您好!

我使用的 D-FF 在应用中具有指定的器件型号。

为了检查器件是否正常工作(缺少 EVB)、我将器件焊接在我设计的 PCB 上、并开始使用最先进的93K 测试头对其进行测试。

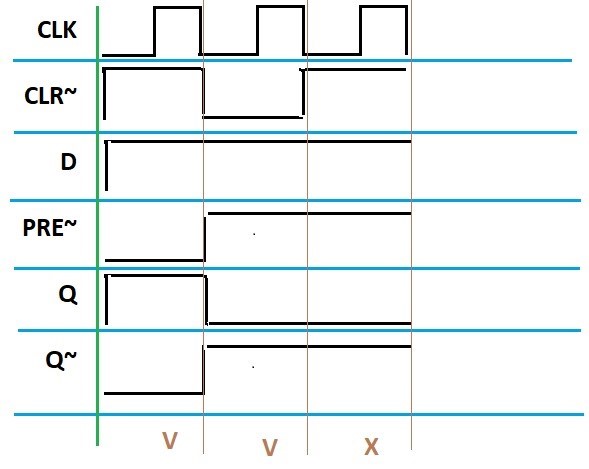

我首先验证表1。 (函数表)逐行显示在 DS (第15页)中、无法使其正常工作。

我从 PRE~低电平和 CLR~高电平开始、因此我得到了 Q=H (正如预期的那样)

然后、我施加了 PRE~ High-Z 和 CLR~ Low 并得到 Q=L (如预期)。

然后、我施加了 PRE~ High、CLR~ High 和1MHz 50%直流 时钟和开始改变 D (H - L - H - L)- Q 未按预期改变。

有些器件既不响应 D 高电平和 D 低电平、也不响应 D 低电平。

我想知道更改 D 引脚是否有特定的顺序、或者我是否必须提前执行某项操作。

谢谢你。