请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TXB0304 Thread 中讨论的其他器件: TXB0104

通过180mm 布线将2MHz 时钟从 TXB0304UTR 发送到 Xilinx XC3S400AN CPLD 时、会出现严重反射、如所附图片所示。 已尝试以下实验、但 无法解决问题:

- 在 TXB0304附近添加串行电阻器(10、20、30、50、100 Ω)

- 在 TXB0304 VCC 附近添加10pF+100pF+47pF 电容器

- 在靠近 CPLD 的 CLK 至 GND 之间添加10pF,100pF,47pF 并联电容器

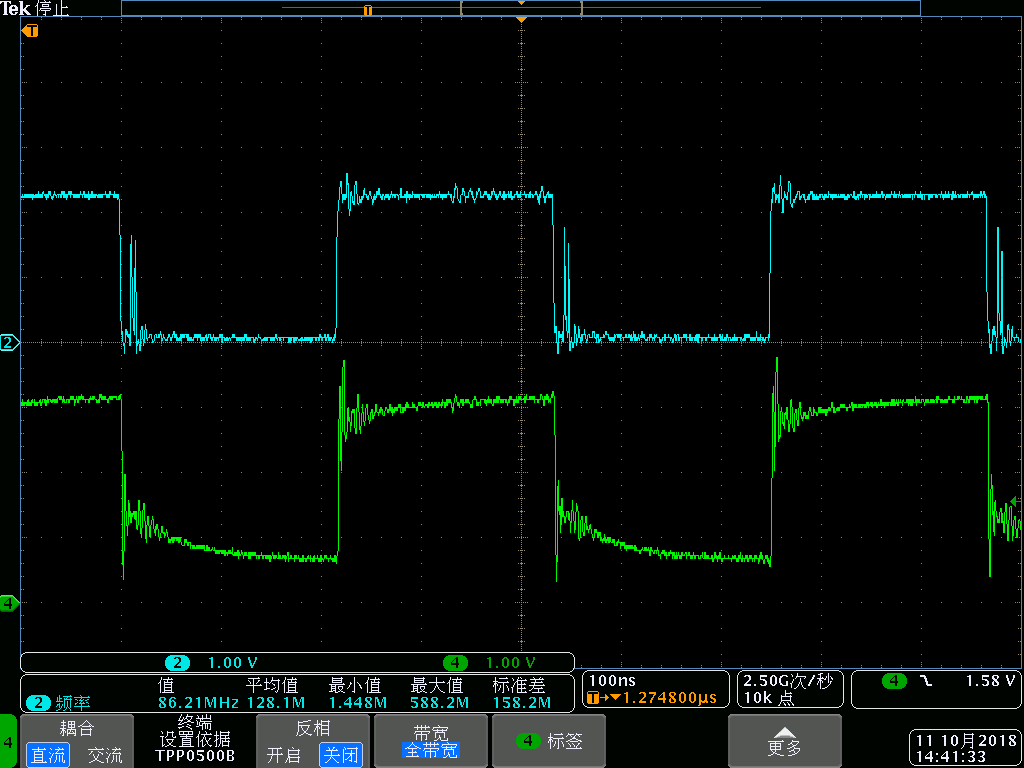

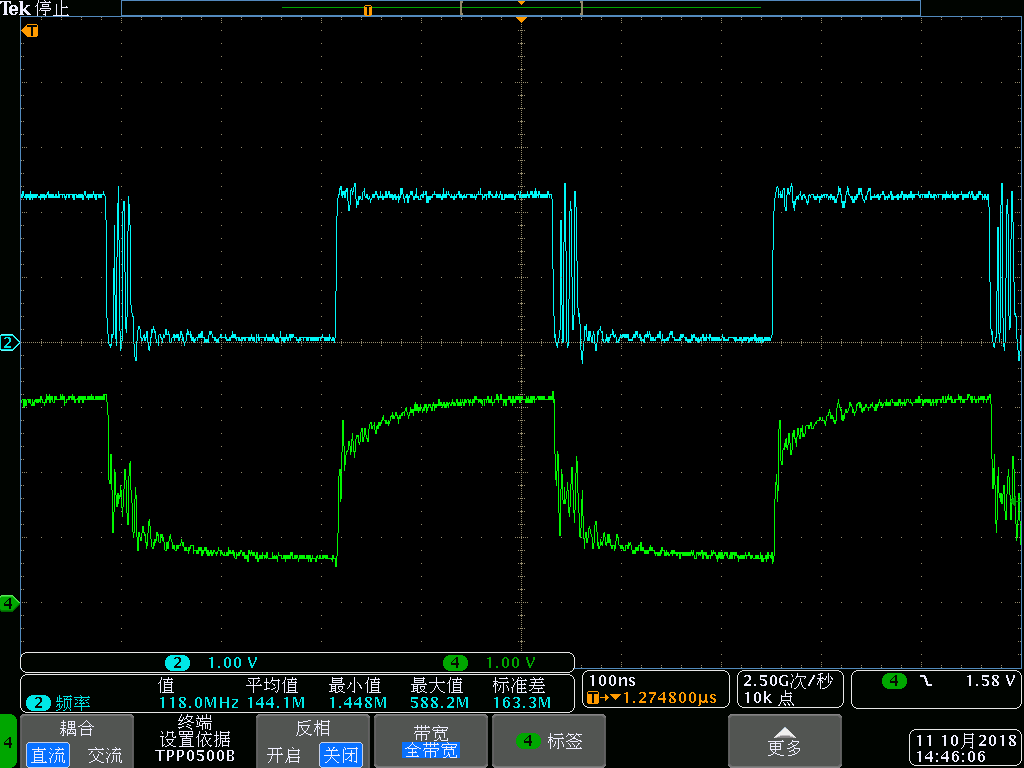

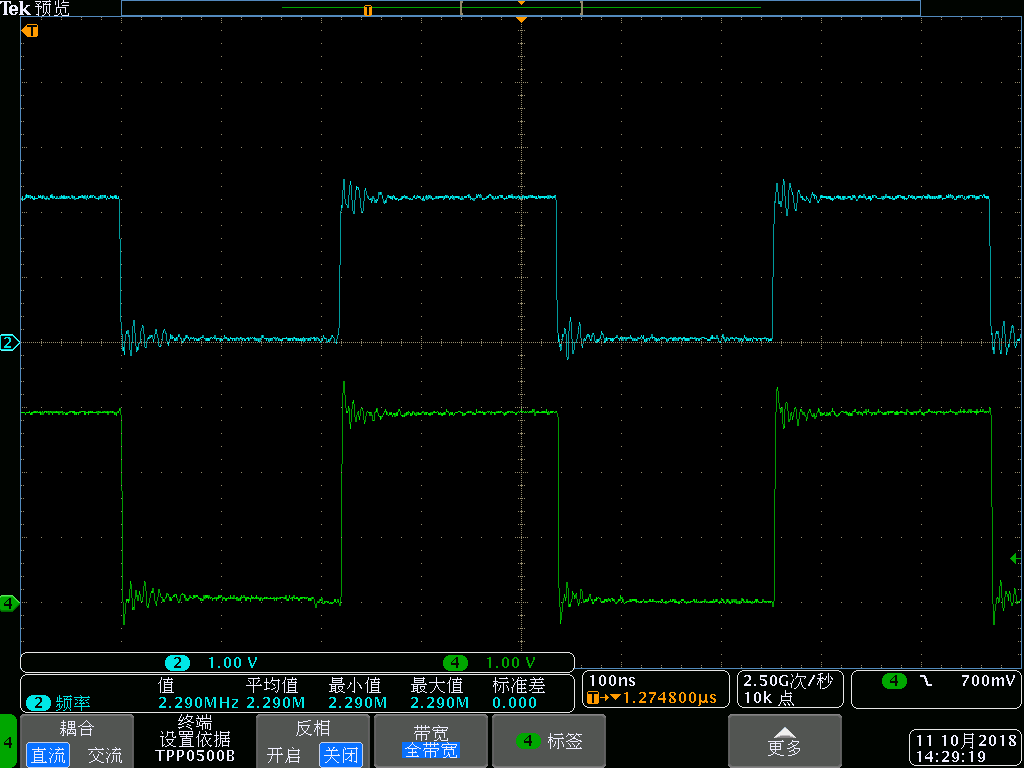

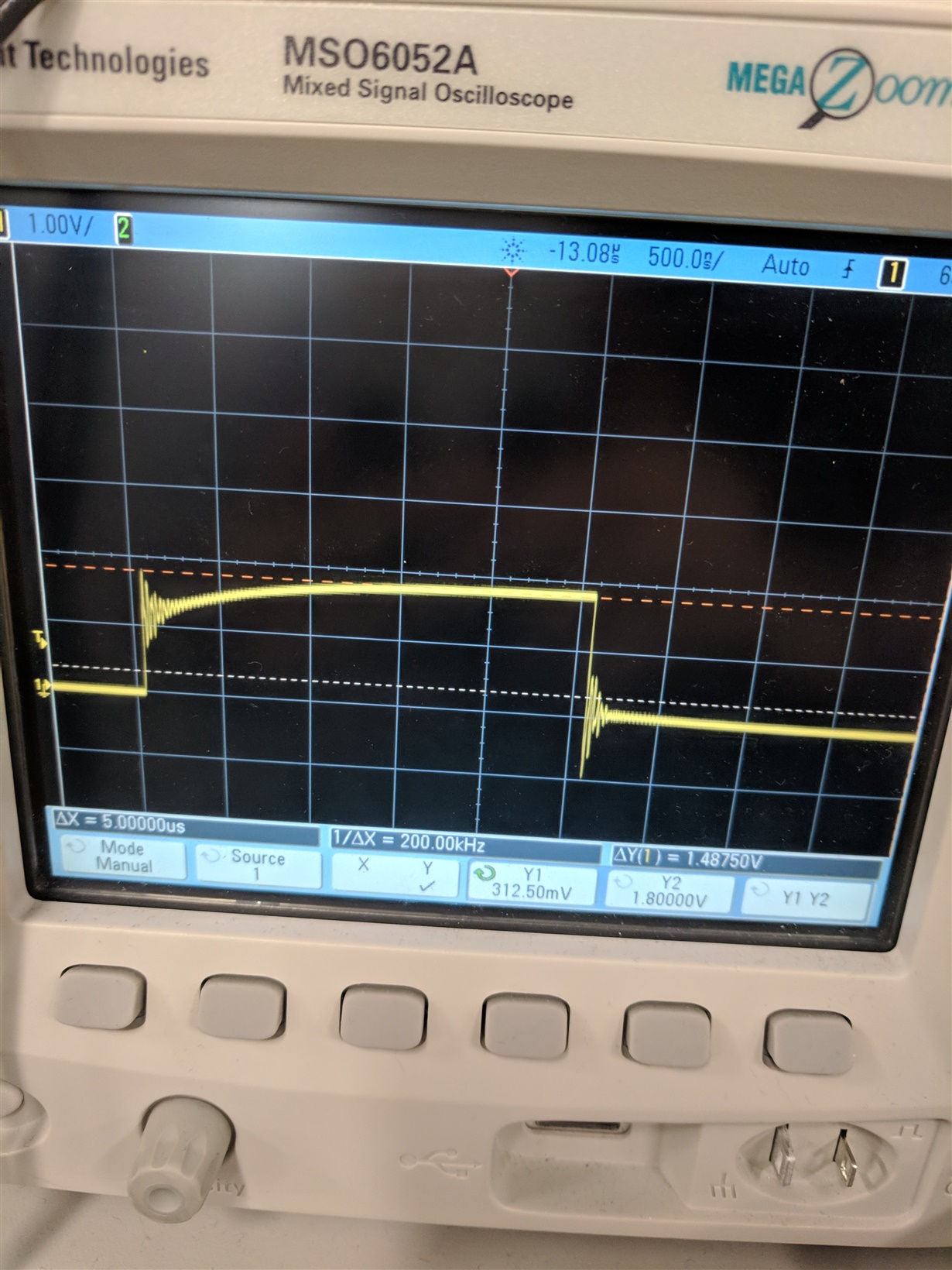

在图中、蓝色波是输入信号、绿色波是输出信号。

图 A 、串行电阻器值0Ω Ω

图 b 、串行电阻器值50Ω Ω

图 c、 串行电阻器值150Ω Ω

图 d、 串行电阻器未 焊接