请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G126-Q1 主题中讨论的其他器件: SN74LVC1G125-Q1、 SN74LVC1G3157

双 SN74LVC1G126-Q1用法

您好!

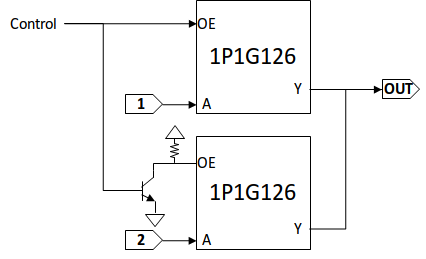

我的客户会使用两个 SN74LVC1G126-Q1作为 SPDT 开关、如下图所示。

在该电路中、需要注意的一点是、由于延迟变化导致的输出信号冲突。

这意味着 、如果我们的器 件具有最小使能延迟(10)、而器件具有最大禁用延迟(反之亦然)、则输出信号可能会发生冲突。 您认为情况是这样吗?

除上述内容外、您还有其他需要注意的问题吗?

谢谢、

Ken