https://e2e.ti.com/support/logic-group/logic/f/logic-forum/750605/sn74lvt125-q1-messy-rising-edge

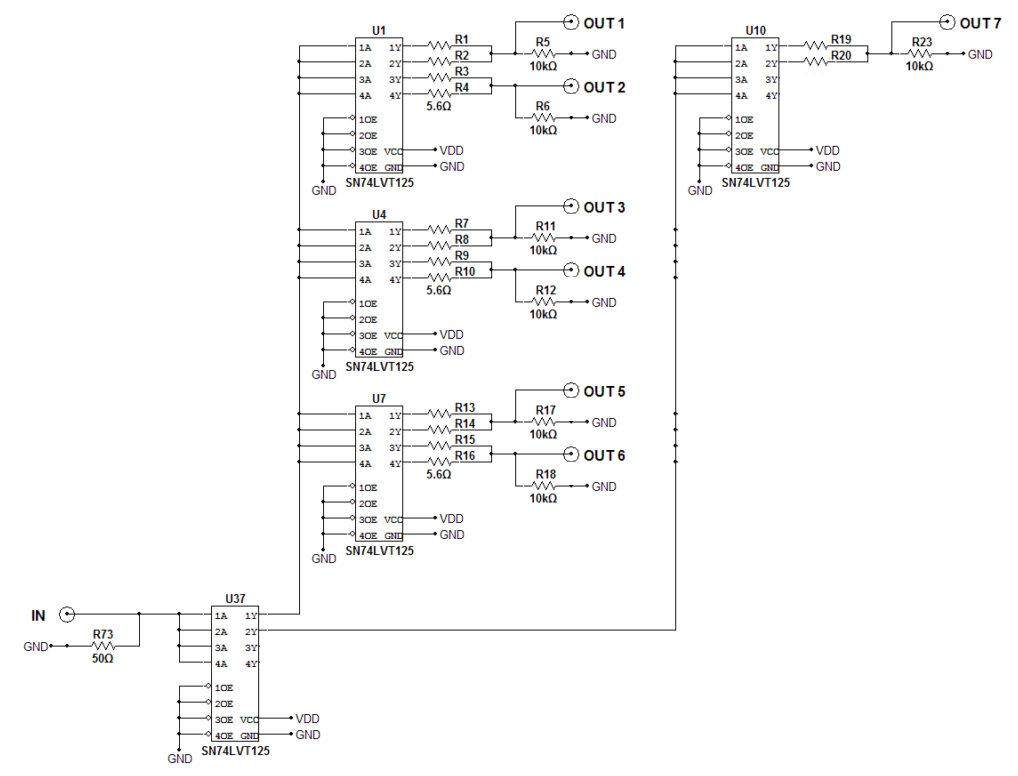

器件型号:SN74LVT125-Q1我将在以下原理图中使用 SN74LVT125-Q1:

此原理图中未显示一个相当大(2.2微法拉)的电容器、我将其放置在电源和接地之间以过滤输入电源、这有助于清理输出波形。

此设计的目的是在四个输出中的每一个输出上重复一个输入信号、同时将电压纹波和上升时间降至最低。

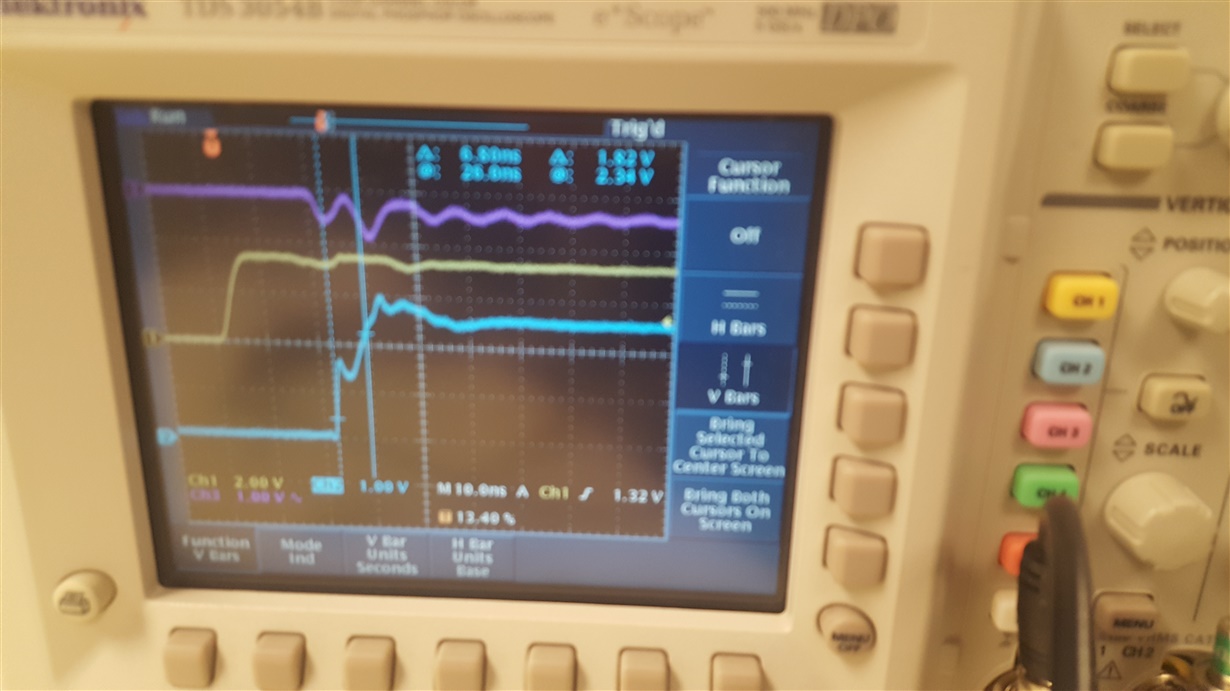

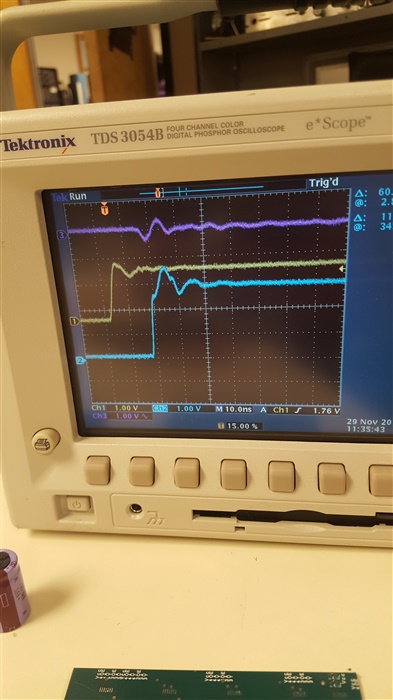

但是、我仍然发现一个上升沿和波形的问题、这对我来说太麻烦了。 这是波形的图片。 电源为紫色、输入为黄色、输出为底部的蓝色波形。

我发现输出中的初始"凸点"即使在电源和接地之间具有非常高的电容且接近1mF 的情况下也是持久的。 您使用了哪些电路来最大限度地降低输出信号的噪声? 我尝试在输出电路上使用基本 RC 滤波器;虽然这有助于降低电压纹波、但这不会影响初始输出"凸点"。

感谢您提供的任何见解。