https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1197664/sn74lvc1g373-sn74lvc1g373yzpr

器件型号:SN74LVC1G373e2e.ti.com/.../SOM-CARD_5F00_20230217_5F00_LA.pdfSN74LVC1G373SCH 评论

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1197664/sn74lvc1g373-sn74lvc1g373yzpr

器件型号:SN74LVC1G373e2e.ti.com/.../SOM-CARD_5F00_20230217_5F00_LA.pdfSN74LVC1G373SCH 评论

您好、Leo、

[引用 userid="553169" URL"~/support/logic-group/logic/f/logic-forum/1197664/sn74lvc1g373-sn74lvc1g373yzpr/4516118 #4516118"]我是否知道哪个引脚需要 去耦电容器?、VCC 引脚?[/quot]是的、任何逻辑器件的 VCC 都应该有一个0.1uF 旁路电容器。 从数据表中:

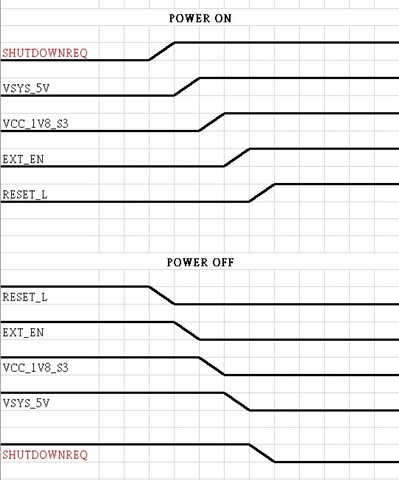

上电时、EXT_EN 将为高电平、输出将为高阻态模式、

断电时、RESET 将为低电平、EXT_EN 将为低电平、 OUT Put 将为低电平以关断载板电源

[/报价]我不确定此电路是否符合您的预期。 上电时的 Q 输出(VCC_1V8_S3打开)未知-锁存器在加载数据之前没有已知的输出状态。

仅当 Q 恰好在高电平状态下启动时、信号 RESET_D 才会产生影响、此后它将不再产生影响、因为锁存器将保持在低电平状态。

当 Q 处于高阻抗状态时、到 VCC5V0_SYS 的上拉将导致输出变为5V、但这不会将 LATCH 状态设置为高电平-一旦输出再次启用、它将被拉回到0V。

当系统上电时、我们希望 shutdownreq 保持高电平、shutdownreq 连接到我们的载板5V EN 引脚。

当系统断电时、我们希望在 EXT_EN 更改为低电平后关断请求、将关断请求输出更改为低电平状态、从而关闭5V EN 引脚。

EXT_EN 该引脚可以显示我们的 PMIC 状态、 EXT_EN 高电平是系统开启、 EXT_EN 低电平是系统关闭

上电时的 Q 输出(VCC_1V8_S3开启)未知->我的输出具有 PU RES、我认为它将保持高电平、我们仅将系统关闭、该电路将处于活动状态、 当 EXT_EN 变为低电平时、输出 Q 也变为低电平以关断载板电源 EN 引脚

锁存器的初始状态未定义;请参阅 [常见问题解答]锁存器件的默认输出是什么? (触发器、锁存器、寄存 器)如果锁存器的初始状态恰好为低电平、则它将主动将其输出驱动为低电平、并且上拉电阻器将不起作用。

锁存器由 VCC_1V8_S3供电、因此只有在 VCC_1V8_S3上电时、其输出才能变为高电平、并且必须在 VCC_1V8_S3断电时下降。 但 VCC5V0_SYS 上拉电阻器意味着当锁存器断电时、输出将被拉高、因此当 VCC5V0_SYS 上电/下电时、SHUTDOWN_REQN_5V 信号将上升和下降。

VSYS_5V 是否与 VCC5V0_SYS 相同?

在您的时序图中、您已在不同的时间显示了所有边沿。 但这是不可能的;SHUTDOWN_REQN_5V 只有在(至少)其中一个输入发生变化或电源发生变化时才能更改。 请具体说明 SHUTDOWN_REQN_5V 的值如何由其他四个信号/电源确定。