嗨、大家好!

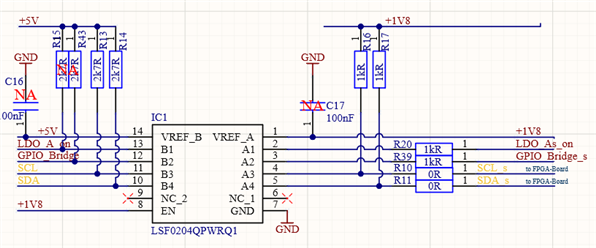

I μ A`m LSF0204QPWRQ1实现从5V 至1.8V 侧的降压转换。

两个引脚用于 I2C (B3、B4)、B1、B2是来自 uC 5V 侧的 GPIO 引脚。

问题是我在引脚 A1/A2 1.97V 处测量、但 VREF_A 为1.80V。

0.2V 的增加来自哪里、或者我可以做什么?

1V8电源轨上没有任何其他会消耗电流的东西。 我曾尝试焊接一个2kR 电阻器、以防有电流流入源极、从而使我的1.8V 电压轨保持水平。 但没有区别、仍然是1.97V。

有任何提示或建议吗?

谢谢。

Markus