主题中讨论的其他器件:SN74AUP1G04、SN74AUC1G04 、SN74LVC1G240

数据表指定了低至1.5V 的"只数据保持"。 我们的理解是、这意味着如果电源降至1.5V 至1.65V 范围内、电路将使输出保持在相同的电平。

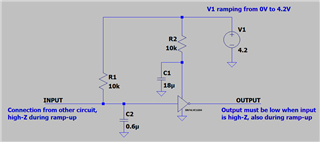

1) 1)但是、在考虑升至1.5V 至1.65V 范围时、是否还有预期的行为?

升高电压时、如果输入(A)保持在(或略高于)电源电压、则...

2) 2)通过1.5V 电压时、预期会出现什么行为?

3) 3) 通过1.65V 电压时的预期行为是什么?

例如、它是未定义的吗?或者我们是否应该假定即使输入与电源一样高、输出也会变为高电平?