主题中讨论的其他器件:SN74AUC2G34、

团队、

我正在使用 电路板上的 SN74LVC2G04DCK 双缓冲器输出器件将25MHz 时钟输入缓冲到两个25MHz 输出中。

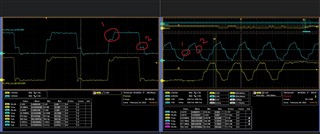

但我看到输出波形完全失真、如下所示。 一个在 R2091串联电阻之前、另一个在串联电阻之后。

输出中出现了某种过冲和下冲、这也反映在我的终端应用 RGMII TX/RX 时钟中。

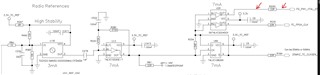

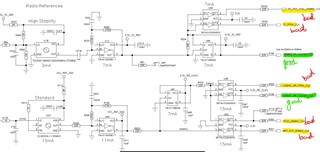

下面是其原理图(我在原理图中已用红色箭头标记、在其中我探测了信号)

请帮助我提供克服这一问题的建议和指导。

谢谢

Pradeep。 秒

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

团队、

我正在使用 电路板上的 SN74LVC2G04DCK 双缓冲器输出器件将25MHz 时钟输入缓冲到两个25MHz 输出中。

但我看到输出波形完全失真、如下所示。 一个在 R2091串联电阻之前、另一个在串联电阻之后。

输出中出现了某种过冲和下冲、这也反映在我的终端应用 RGMII TX/RX 时钟中。

下面是其原理图(我在原理图中已用红色箭头标记、在其中我探测了信号)

请帮助我提供克服这一问题的建议和指导。

谢谢

Pradeep。 秒

"之前"是指"左侧"吗?

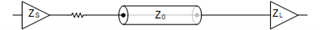

"之前"波形中的振铃是无害的。 "之后"波形中的反射不是这样的、并且可能是由端接不当引起的。 请参阅 [FAQ]将逻辑器件的输出连接到50欧姆的传输线路时会发生什么情况?

您的布线的特性阻抗是多少? LVC Ω 非常强(3.3V 时约为12 Ω)、因此我怀疑22 源端接电阻器可能过低。 Ω 33 μ F。

U29和 R2091之间的布线长度是多少? 应尽可能短。

您真的使用50 Ω 输入测量了吗? 这与您的器件的高阻抗时钟输入的负载不同。

您好、Clemens:

非常感谢您的帮助。

是的、我是说左侧意味着在串联端接之前。 从 U29到 R2091的布线长度仅为25mil、Zo 为44.315 Ω。

让我尝试使用其他串联终端值33E。

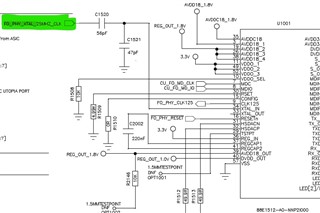

缓冲器的时钟输出 连接到 Marvell PHY 88E1512 XTAL 输入引脚、下面是其原理图 、在连接到 XTAL 引脚之前、通过电容分压器将3.3V 转换为1.8V 时钟。

希望这可能不是缓冲器的上升/下降时间限制造成的。 如果有任何建议、敬请告知。

谢谢。

Pradeep。 秒

您好、Clemens:

快速、我在更改33E、11E、0E 不同的串联端接电阻后也进行了测试。

波形仍然不正确。 信号变得更糟,(抱歉,我现在无法连接信号...)

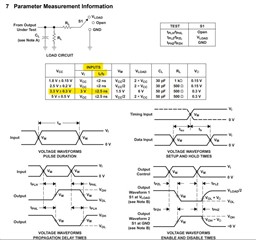

我想这可能是由于驱动强度还是上升/下降时间。 您能否提供输出引脚的上升/下降时间限制、因为数据表中仅提供输入上升/下降时间规格、如下所示。

由于您为此应用建议了不同器件、我们将尝试检查可行性。 但我们很可能计划重复使用这个现有的缓冲区。 那么、是否仍可以通过某种方式来使用此器件并进行一些优化、从而满足所需的输出?

请寻求您的建议。

谢谢。

Pradeep。 秒

您好、Clemens:

我已经尝试使用电阻122ohm、150ohm 以输出1.8V 电压来替换电容器。

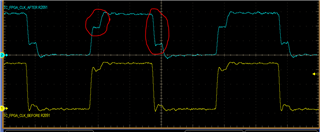

但我在缓冲器输出上看到了类似的波形、观察到的变化不大。 另外、下面是进入 Marvell PHY 作为基准输入时钟25MHz 的缓冲器输出时钟的波形、右侧的波形是使用该25MHz 时钟在 Marvell 芯片上生成的 RGMII RX 时钟。 25MHz 下的波形失真也直接反映在 RGMII RXCLK 中。

我想在这里补充一点、在电容分压器之后、我们可以看到1.8V 时钟 的效果更好、如下所示。但是我不清楚电容分压器之前的失真波形现在是如何反映在我的终端 RGMII RXCLK 波形中的。。。。

请帮我提供您的建议。

谢谢。

Pradeep。 秒

Pradeep、您好!

此处显示的"气压步进"信号:

是由您正在驱动的传输线路导致的。 信号沿线路传输并返回所需的时间、此时间等于信号在中间状态暂停的时间。

这是信号在缓冲器输出端的样子(在上图中的 Z_S 和 R 之间)、但这并不是实现良好的信号完整性很重要的方面-在接收器件(在 Z_L 处)具有良好的信号完整性很重要。

假设您的输出阻抗与线路阻抗相当匹配(相当接近)、您应该不会在接收器件上看到任何明显的问题。

遗憾的是、我无法通过论坛教授所有有关传输线理论的知识-这是一个非常复杂的主题。 可以这么说、如果远端的信号看起来很好、那么系统就会正常工作。

尊敬的 Emrys:

感谢您的引导、为我提供了详细的信息。

此外、我在设计中发现了另外一个可能导致此处出现问题的因素、但我不确定。

SN74LVC2G04中的缓冲输出时钟、指向我们电路板中最远的 FPGA、但这些时钟的波形仍有阶梯状。 接近最近的 PLL AD9576的基准时钟输入引脚的相同缓冲器输出没有阶梯、而是非常好、正如我在随附的 Excel 中显示的、该输出将所有信号与其迹线长度、灌电流、源细节进行了比较。 请检查一次。 此外、还可以在此处找到原理图。

e2e.ti.com/.../TI_5F00_Buffer_5F00_output_5F00_waveform_5F00_comparision.xlsx

我认为、低于2000mil 的布线长度似乎较好、但在7000mil 以上的布线会出现问题。 那么、该问题是否仅与冗长的布线长度有关??? 请征求您的意见。

谢谢。

Pradeep。 秒