https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1263280/sn74lvc07a-output-low-fixed-issue

器件型号:SN74LVC07A您好!

请告诉 我 TI 对于以下内容的观点?

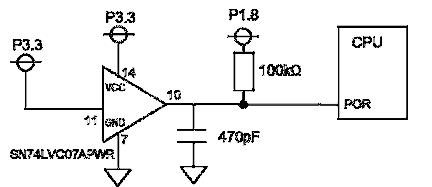

对于图中所示的电路配置、

即使输入侧(引脚11)为高电平、输出侧(引脚10)仍处于低电平、然后切换输入不起作用。

经调查后、电源序列为 P1.8→P3.3、并在为 SN74LVC07APWR 供电之前为引脚10上拉提供1.8V 电压。

这是否会导致 SN74LVC07APWR 发生故障?

但是、同一个电路由相同 SN74LVC07APWR 的13个引脚和12个引脚组成、但是对于输入侧(13引脚)的 H 输入、输出侧(12引脚)也输出到 H、并且它正常工作。 。

(1)如果在为 SN74LVC07APWR 供电之前向其施加了电压负载、那么 SN74LVC07APWR 是否会发生故障(如上所述)?

(2)如上所述、同一 IC 是否可能因引脚而出现故障或不发生故障?

关于上述客户投诉、当我查看数据表中的绝对最大额定值时、似乎在电源之前为开漏上拉电阻供电没有问题。

此致、

广志