主题中讨论的其他器件: SN74HCS165

大家好、

客户表示在新的批处理板中使用 SN74HC165时出现错误。

他们读取板 ID、但出现问题。板 ID 为10001101、但读取的是00011011。 以下是他们的原理图。

我在旧批次测试他们的电路板、波形在后面、保持时间为14ns。 在其板中、采样点是上升沿。

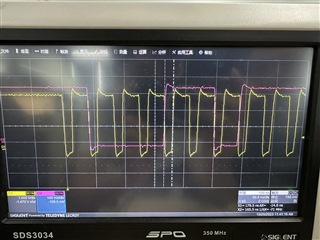

以下是他们的新批次、保持时间为11ns。 这是两个批处理设备之间的主要差异。 所有器件均为2022年第2季度之后客户购买的器件。

我们建议客户更改 PCB 或固件。 但它们很难更改这些设置。

有没有其他方法可以解决这一问题?

非常感谢。