请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G11 您好

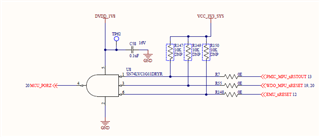

我们 在基于 AM625x 的设计中使用了 SN74LVC1G11DRYR。 我们已将该与门用于复位逻辑。 以下是我们的实施方案、

我们面临的问题是、连接到引脚6的信号(emu_reset 是在连接到 XDS110调试器时从外部驱动的信号)置于低电平时、 与门的输出不会变为低电平。

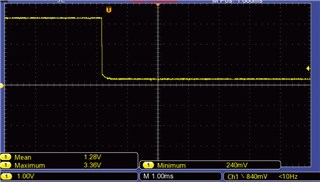

我们已为 EMU 复位信号提供了4.7K 上拉电阻。 以下是我们探测 emu 复位时的波形、

我们尝试提供各种其他上拉选项,也使 VIL 小于240mV ,但与门仍然没有识别到这种低电平,并且 O/p 总是高电平。

为了检查与门、我们通过移除串联电阻器并将其拉低来隔离 emu 复位信号、以查看输出电压是否变为低电平。 我们按预期观察到输出低电平。

我们想知道当 emu 复位信号(3.3V 信号)连接到与门(由1.8V 供电)时为什么会引发问题? EMU 复位时 I、e 逻辑低电平不被驱动为与门的 O/p 上的逻辑低电平