大家好、我正在从事一项使用5V 微控制器的设计、该微控制器需要连接到3.3V 存储器。 为此、我添加了一组 LSF0108。 出于测试目的、我没有任何元件连接到低端(A)、使用微控制器、我可以使用 GPIO 来设置每个 B 侧输入。 当 GPIO 为低电平时、A 侧也为低电平、到目前为止一切正常。 但是、当 GPIO 变为高电平(5V)时、A 侧变为大约4V。 同样、这是在没有连接负载的情况下进行的。 我正在使用的存储器芯片指定其输入电流最大值为1uA、因此我认为没有必要上拉。 为了模拟该负载、我在 A 侧接地连接处添加了一个1.5M 的电阻器。 然后电压降至3.5、最高3.8V。 我 恐怕要在 PCB 上焊接存储器芯片、因为较高的电压可能会损坏器件。 那么、A 侧上的电压为什么如此高且未被钳位到3.3V 基准电压?

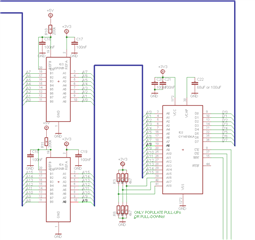

这是原理图:存储器 IC 为 CY14B104