主题中讨论的其他器件: SN74LVC1G125

您好!

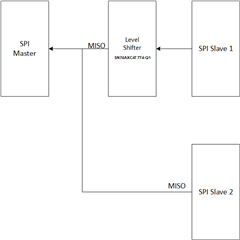

器件中配置的 SPI 器件如下所示。 MISO 线路从电平转换器输出。

当 SPI 从器件2驱动 MISO 线路时、按预期工作。

当 SPI 从器件-2驱动 MISO 线路时、MISO 信号仅高达0.4V (IO 逻辑为1.8V)。 SPI Salve-2无法将 MISO 线路驱动为高电平。 电平转换器强烈将 MISO 线路驱动为"低电平"。

当电平转换器与 SPI 总线隔离后、SPI 从器件-2 MISO 线路按预期工作(1.8V 电平)。

使用 SN74AXC4T774-Q1时、这是否是预期的行为?