主题中讨论的其他器件:CD4093B、CD4044B 、 TL7733B、 TPS3710、TL7700-SEP

附加的是我们的电路;一个由 CD4093B 内的两个与非门配置的著名 RS 触发器。 出于某些未知原因(幸运的是)、只要加电、它始终处于所需状态(nQ 为高电平)。 但是、我要确保输出始终处于该状态。 到目前为止,他们有,但我不知道为什么。

我认为我可以做的是延迟 nr 输入的上升、以使其相应的输出(nQ)变为高电平。

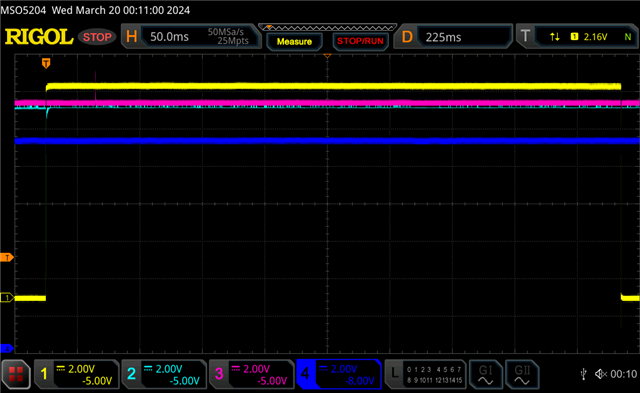

为了在试验电路板电路中实现此操作、我在该输入的上拉电阻器(R13)和电容器(C12)(请参阅随附 zip 文件中的原理图)。 这样做会导致整个电路无法工作。 如果我将它们从电路中移除、那么它将返回所需的功能。 然而,在 LTSpice 模型(原谅我! 电路根据需要执行瓶胚。 这就是我并不总是信任仿真的原因。 我感到困惑。 我通过查看电路的其他部分来查看它们是否对触发器产生影响、但到目前为止、我找不到任何结果。

如果您想了解它的工作原理、我已经在随附的文件中包含了一个 PDF 和电路模型(以及所需的子电路)。 如果有任何需要、我可以做些什么来确保电路每次处于所需状态(见下文)? 这个问题现在已变得紧迫。 因此、我们非常感谢您所能提供的一切。 非常感谢! W. Probasco、908-246-3873