主题中讨论的其他器件: DP83867IR

工具与软件:

我很想了解在千兆以太网配置中通过 TXV0106电平转换器驱动 DP83867IR 的 RGMII 时、如何达到 RGMII v2.0时序规格。

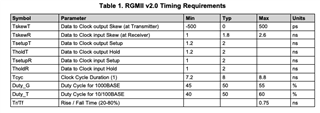

使用 TI 应用手册 SNLA243–2015年10月作为 DP83867时序预算的参考时、我得到以下时序:

MAC-IOSKEW 设置= 2ns -- Rx = 2ns -0.2ns - 0.35ns = 1.45ns

MAC-IOSKEW 保持= 8ns *(1-0.05-0.5)- 2ns -- Rx = 3.6ns - 2ns -0.2ns - 0.35ns = 1.05ns

MAC-Tx 设置= 2ns - Idvar - IOskew - minTsetupRx = 2ns - 0.2ns - 0.35ns - 0.5ns = 0.95ns

MAC-Tx 保持= 8ns *(1-0.05-0.5)- 2ns - Idvar - IOskew - minTholdRx = 3.6ns - 2ns -0.2ns - 0.35ns - 0.25ns = 0.8ns

现在、TXV0106电平转换器在我的应用中向时序预算引入了+/-0.3ns 的偏斜:

MAC-MAC Rx 设置裕度= 1.45ns - 0.3ns = 1.15ns

MAC-MAC Rx 保持裕度 = 1.05ns - 0.3ns = 0.75ns

MAC-Tx 设置裕度= 0.95ns - 0.3ns = 0.65ns

MAC-Tx 保持裕度= 0.8ns - 0.3ns = 0.5ns

尝试在 Altera Cyclonve V FPGA 上安装 MAC/RGMII 驱动器失败、因为存在这方面的限制。

此电平转换器开发了哪种 MAC/RGMII 驱动器? 您能否 在不违反时序预算的情况下共享一个使用该 TXV0106的系统?