请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G32-Q1 主题中讨论的其他器件:SN74LVC1G08

工具与软件:

团队成员、您好!

我会收到一个后续问题、该问题已通过该主题关闭: https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1404713/sn74lvc1g32-q1-input-transition-rise-fall-time/5377355#5377355

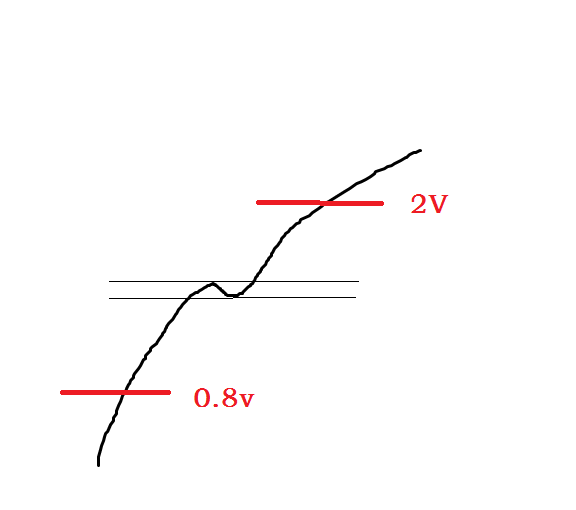

假设我们正在研究从低电平到高电平的转换、数据表显示栅极在3.3V 电源(例如 SN74LVC1G08)上的2V 输入电压最新情况下检测到高电平。 因此、我知道我们需要确保我们没有超过33ns 的时间来达到2V 阈值? 之后、该行为就无关紧要了、因为 IC 内部已经发生了转换?

感谢您的支持和此致、

Michael