主题中讨论的其他器件:TXU0204

工具与软件:

您好!

我们正在使用电平转换器将逻辑 UART 电平从1、8V 传输到3、3V。 使用我们的旧控制器、我们没有出现高 Iq 问题。 现在、在控制器切换之后、我们在具有高阻抗输入的 UART 引脚上获得了高 Iq、我们在这种情况下会提出不同的控制器行为、但这可能是连接在顶部的线程。

对于我的问题:

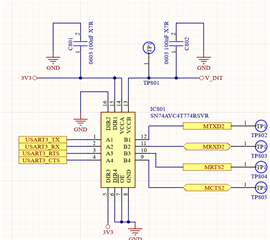

目前、我们将 OE 接地、将电平转换器设置为常开。 在数据表中、OE 可设为高电平以禁用器件。 然而、不清楚的是、当使用100k 上拉电阻时、将器件保持在停用状态所需的功率大小。 原理图如下所示。

此致