工具与软件:

大家好、团队成员:

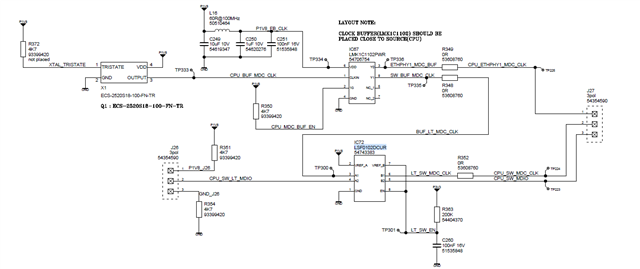

对于 MDC、使用电平转换器 LSF0102DCUR 1.8V 至3.3V。

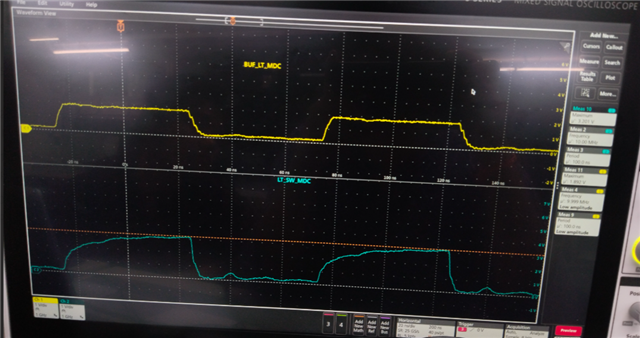

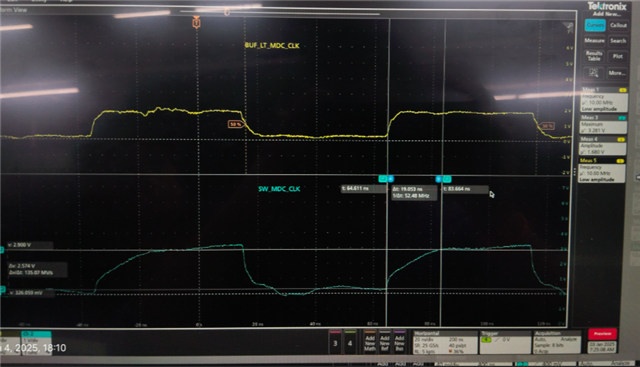

1.从外部添加引脚 A1输入4.7K 上拉至1.8V、从外部添加引脚 B1输出1K 上拉至3.3V

引脚 A1最大电压为1.68V、引脚 B1最大电压为3.28V

2. 在外部添加引脚 A1输入1K 上拉至1.8V、在外部添加引脚 B1输出1K 上拉至3.3V

引脚 A1最大电压为1.89V、引脚 B1最大电压为3.2V

请建议输入电压为1.8V、输出电压为3.3V。

谢谢!

Vidhya