主题中讨论的其他部件: DRV8251A

您好,

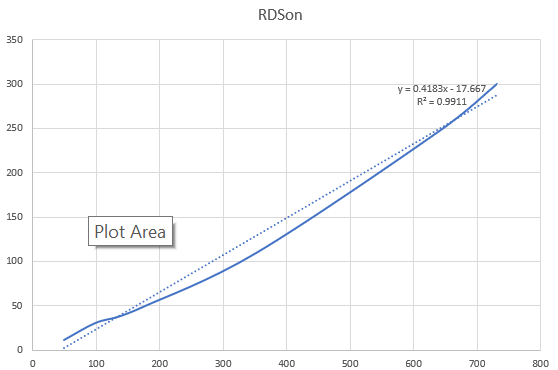

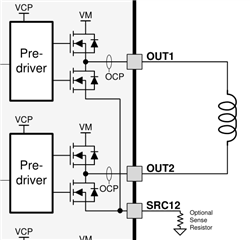

我正在设计一个控制板,用于以~9V工作的双稳态水阀。 我想控制开/关电磁阀电流脉冲(300mA用于250ms或 -50mA (60毫秒),并检测各种异常情况,包括阀存在和端子短路。 为了简化设计,我计划使用1R并联电阻器,并将SRC12/34电压(通过1k)传递给UC的ADC输入(提供1.1V的VREF,允许最大5V电压)。

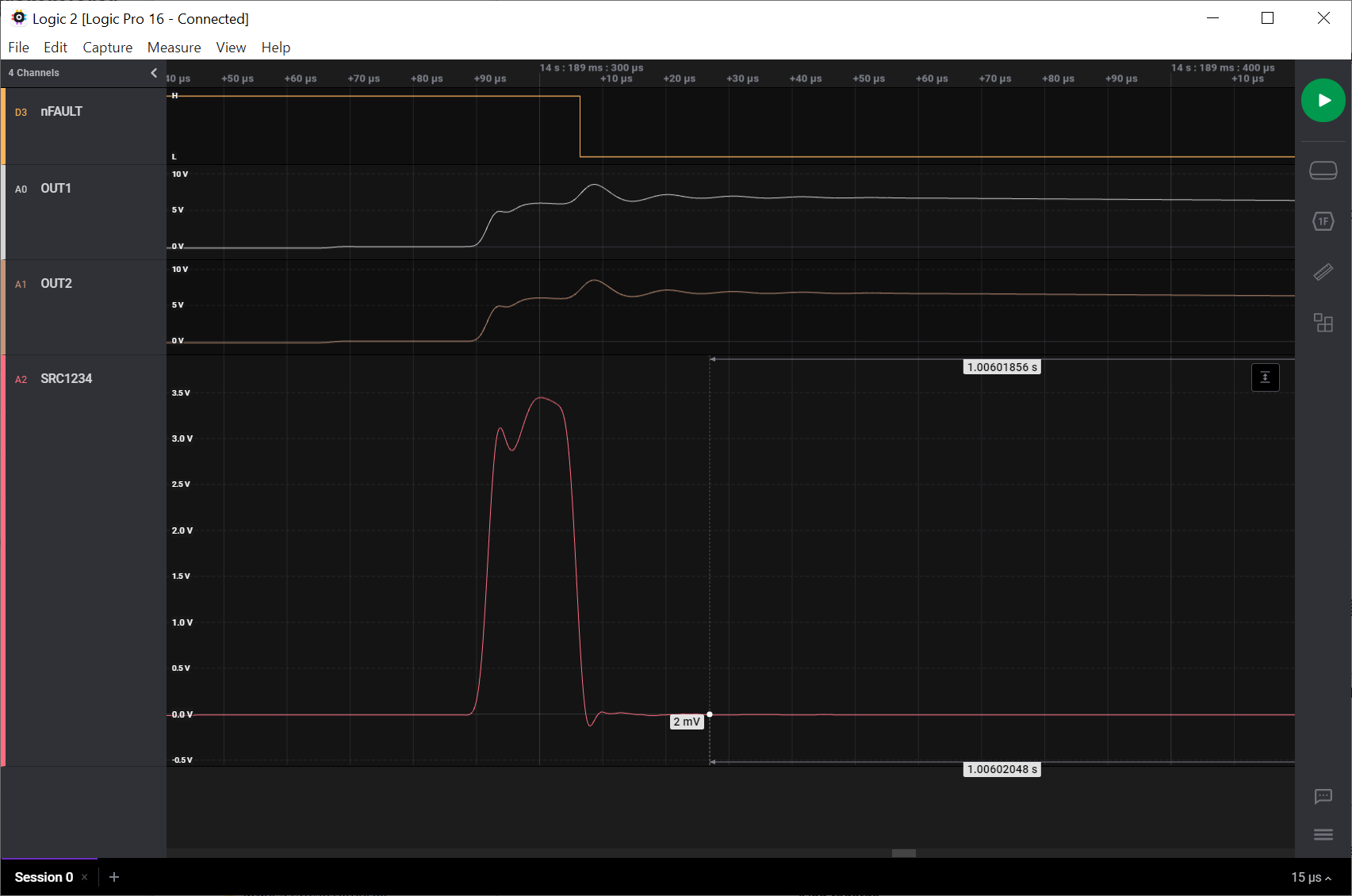

现在,端子短路我观察到SRC12/34的电压在15us时上升到3.5V,然后DRV8844的过流保护启动,从而关闭FET。

但根据数据表,SRC12/34的最大电压为+-0.6V。 此数据表最大电压要求我使用更小的并联电阻器(例如0R1),因此以这种简单的方式限制了我的能力监控器与UC的电感电流上升(以便检测电磁阀存在)。 相反,我可能需要在主板上添加SRC12/34信号的OPA放大器,从而增加一些噪音。

现在,我假设最大+-0.6V与VNEG相比,FET源受一些钳位二极管的ESD保护。 但根据我的测量,当对终端短路时,SRC12/34的电压*确实*升至3.5V。 怎么会这样呢?

所以我的问题基本上可以归结为:如果我在SRC12/34上超过0.6V,会发生什么情况? 此电压对IC中的哪些部件施加了多少压力? 如果这种情况很少发生,而且很快发生,是否可以接受?

此致,

Sebastian