主题中讨论的其他器件:DRV8305、

感谢您的支持。

我们的客户对 DRV8305NE 的 VDS_OCP 有疑问。

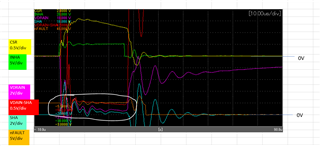

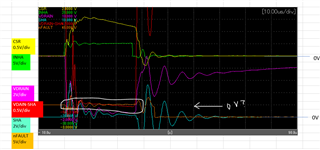

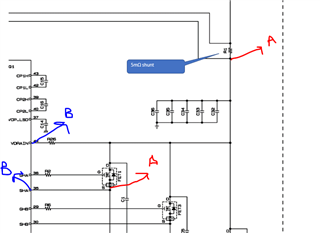

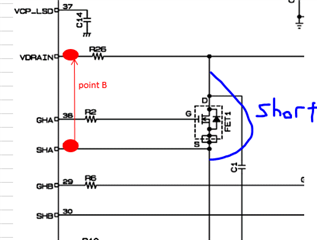

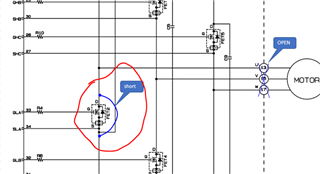

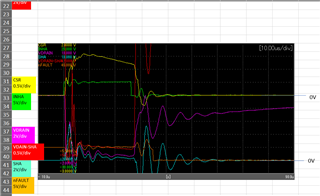

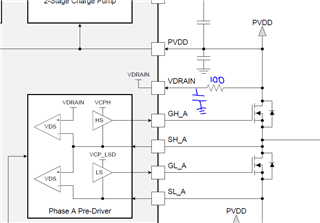

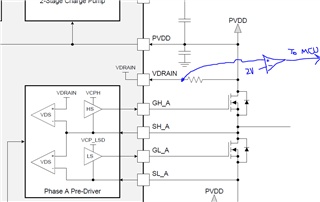

客户在 U 相(IC 的 A 相)的较低级短接了 FET 的漏源,并确认了 MOSFET 过流保护(VDS_OCP)的运行。

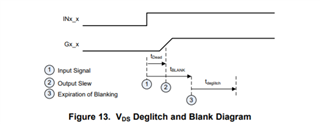

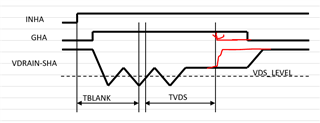

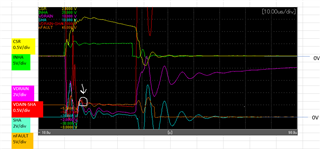

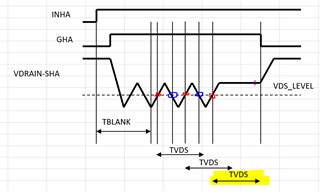

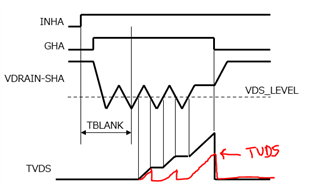

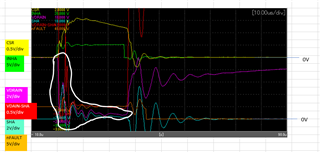

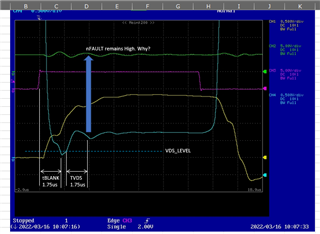

即使 VDRAIN-SHA 的电压在20us 内超过了155mV 的阈值、IC 也未检测到短路。(请参阅随附的 Excel 中的"波形"表)

造成这种情况的原因是什么?

有关寄存器设置、请参阅随附的 Excel 中的"控制寄存器"表。

e2e.ti.com/.../VDS_5F00_OCP.xlsx

此致、

库拉