请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DRV8906-Q1 大家好、

我从客户那里得到以下问题:

当一个输出为低电平、另一个输出为高电平时、两个输出之间的电阻短路会发生什么情况?

电流是否仅在 t_oc 时间内受到 2 x 0.55Ohm 内部漏极电阻的限制?

谢谢、此致

David

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我从客户那里得到以下问题:

当一个输出为低电平、另一个输出为高电平时、两个输出之间的电阻短路会发生什么情况?

电流是否仅在 t_oc 时间内受到 2 x 0.55Ohm 内部漏极电阻的限制?

谢谢、此致

David

嗨、David、

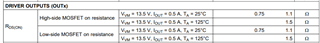

我相信您是对的、在 tOCP 时间(1us 至60us 可选)内、尽管我看到的是0.75Ω rds (on)、但芯片不会主动采取任何措施来限制电流。

您可能还会发现功能安全文档很有趣、尤其是 表4-4。 适用于短路到相邻引脚的器件引脚的引脚 FMA: DRV8906-Q1功能安全时基故障率、FMD 和引脚 FMA。 它指出、当 OUT5到 OUT1等两个输出短接时、负载驱动能力将会丧失。 此文档可在 驱动程序页面的技术文档下找到。

此致、

Jacob