主题中讨论的其他器件: TPS544C20、 LM5066I

工具/软件:

您好、

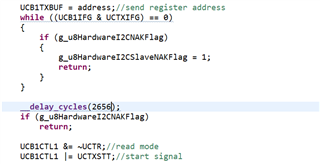

当我使用 MSP430F5529的 I2C 模块时、发生了一些问题。 我使用以下代码来发送一个读取字节信号。 (当前 MCLK 为32MHz)

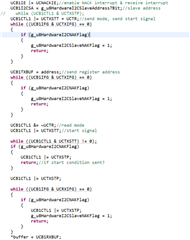

中断代码如下所示

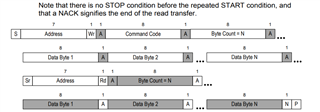

I2C 模块启动后、我启用 NACK 中断、并开始传输读取字节信号。 我要发送的信号如下所示

当我测试是否在重复启动信号之前收到 NAK 回复时、例如、我不希望发生一些事情

我想在接收到 NAK 信号时发送停止信号、在上面的示例中、我想在接收0x00[NAK]后发送停止信号、以下读取信号不会再发送、就像下面一样

我的代码有问题吗? 如何更改代码以实现预期功能并解决此问题?

最好的注意、

ZJY