“线程:测试”中讨论的其它部件

对于我的系统,我有一个10MHz 的晶体。 MCLK 和 SMCLK 都以除以1的方式运行,因此两个时钟都以10MHz 的速度运行。

我的 ADC 在 SMCLK 下运行, ADCPDIVx 设置为00除以1, ADCDIVx 设置为010除以3。 这使得 ADCCLK = 3.333MHZ。

ADC 设置为12位模式,以及4个采样和保持周期,ADCSHTx =0000。

因此,ADC 总转换时间为4 SH +(2 + 12)转换周期= 18个周期总计。

问题是,它大约需要78个周期,如周期计数器所示,而开销所需的周期更少。

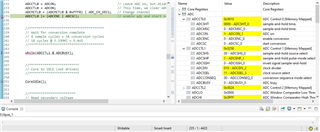

以下是转换开始前第一个断点的屏幕快照。 循环计数已重置为0。

=========================================

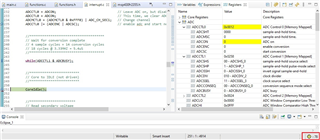

以下是清除占线标志(转换完成)后立即显示的第一个指令的屏幕快照。 请注意78处的循环计数器。

=================================

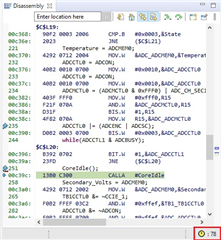

供参考,下面是代码的反汇编视图,以免您认为周期来自其他地方。

=================================

为什么周期数与预期相差太大。 MCLK 和 SMCLK 都以相同频率运行,因此周期计数器应与 SMCLK 周期匹配。