主题中讨论的其他部件: MSP430FR6989

你好

我正在使用带有MSP430FR6.9891万的LaunchPad评估套件。

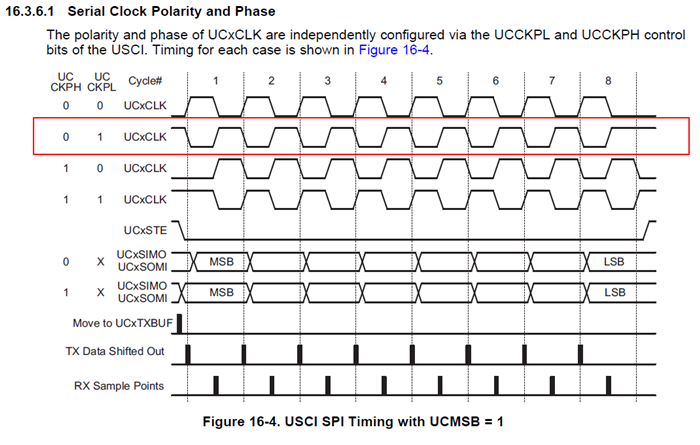

我想在从属模式下使用SPI接口USCIA0,4引脚模式有源高,并启用时钟相位标记UCCKPH=1

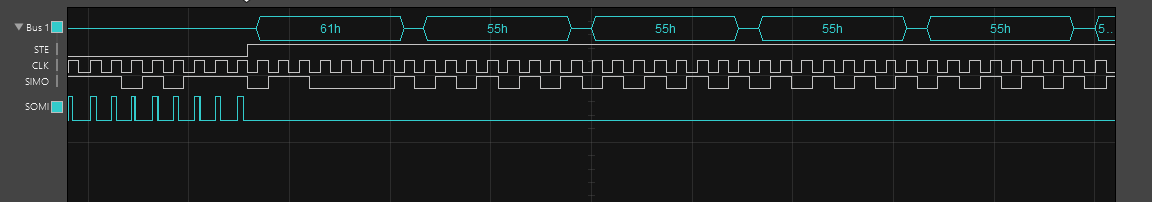

我有UCA0IE设置,也设置了GIE。 在逻辑分析器上,我可以看到UCA0STE引脚变高,时钟工作,数据(SIMO)正确,但中断未激活。

我可以观察到,如果我不设置UCCKPH (UCCKPH=0),中断就会工作,而且如果我使用UCSWRST=0 (不正确)配置SPI接口,它也会工作。

我正在将CCS 7与GNU编译器(GNU 6.2 v.1.16 DOMNIUM技术有限公司)配合使用

此处我的配置:

void初始化Uca0Spi(void){

//为SPI操作配置USI_A0

UCA0CTLW0 = UCSWRST; //**将状态机置于复位**

#IF (RX_MODE ==1)

UCA0CTLW0 |= UCSYNC | UCMSB | UCCKPH | UCMODE_1;

#else

UCA0CTLW0 |= UCSYNC | UCMSB | UCCKPH;

#endif

UCA0CTLW0 &=~UCSWRST;

#IF (RX_MODE ==1)

UCA0IE |= UCRXIE;

__no_operation();

#endif

}

有什么想法?

提前感谢