请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP430F5132 大家好!

我的目标是将 MCLK 设置为8MHz。 在 CCS 中调试时、我在 PJ.1上获得奇怪的输出。 点击"Terminate"停止调试后、时钟在示波器上看起来非常完美。 有什么原因吗?

我将 MCLK 输出到 PJ.1:

PJSEL |= BIT0 + BIT1 + BIT2; //Output CLKs to PJ.0-2 PJDIR |= BIT0 + BIT1 + BIT2;

我的目标是8MHz MCLK 速度:

// configure clocks

UCSCTL3 = SELREF_2; // Set DCO FLL reference = REFO

UCSCTL4 |= SELA_2; // Set ACLK = REFO

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_5; // Select DCO range 16MHz operation

UCSCTL2 = FLLD_1 + 243; // Set DCO Multiplier for 8MHz

// (N + 1) * FLLRef = Fdco

// (243 + 1) * 32768 = 8MHz

__bic_SR_register(SCG0); // re-enable the FLL control loop

// Worst-case settling time for the DCO when the DCO range bits have been

// changed is n x 32 x 32 x f_MCLK / f_FLL_reference. See UCS chapter in 5xx

// UG for optimization.

// 32 x 32 x 8 MHz / 32,768 Hz = 250000 = MCLK cycles for DCO to settle

__delay_cycles(250000);

// Loop until XT1 & DCO stabilizes - In this case only DCO has to stabilize

do

{

UCSCTL7 &= ~(XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

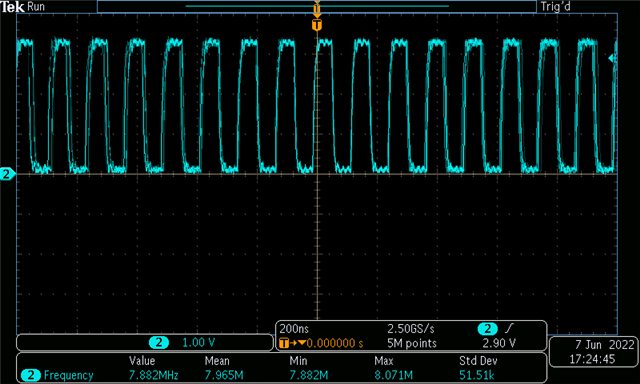

使用 CCS 调试器时、我的示波器会显示奇怪的时钟信号:

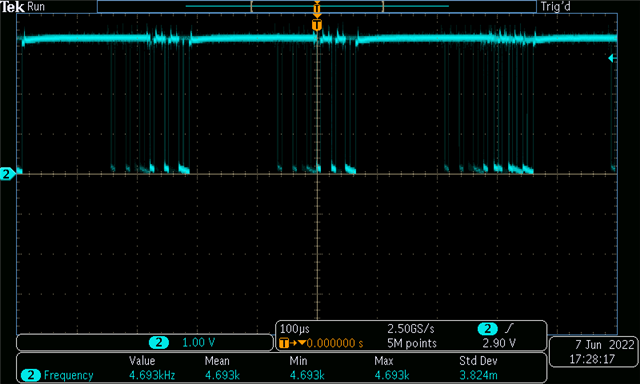

但是、当我单击"终止"时、我的示波器会显示干净的 MCLK、完全符合我的期望: