您好!

我正在尝试通过使用 IAR 7+和 USB-IF 仿真器以及 Spy-Bi-Wire 来调试进入/退出 LPM4.5的汇编代码。

我在 slau138as (表2-1)上看到、FR2433没有 LPMx.5调试支持(即使 调试器选项包含复选框"启用 ULP/LPMx.5调试")、因此、根据 slaa424 (第2章)、我假设我必须通过选择"运行时释放 JTAG"并使"目标运行"选项进入 LPM4.5 (对于 IAR)。 然后、为了从 LPM4.5唤醒(并行 2.3)、当我使用 I/O 端口作为中断源时、我必须在应用程序代码中包含一个软件调试陷阱、例如:

;用于 LPM4.5的软件陷阱

lpm5_wait

bit.w #0x0080,&pain ;--只要执行就会在这里停止

jz lpm5_wait;输入为低电平

;这可用于同步调试器

;并在 LPM4.5之后从此处继续调试

我的问题如下:

1) 1)此过程是否正确以及唯一可用于调试 LPM4.5的过程?

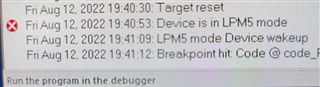

2)不幸的是、当进入 LPM4.5时、即使我通过'run'命令执行(而不是单步执行)、调试器也会失去控制并强制复位。 有什么可能出错的想法吗?

3) Sla424 (第3章)也是指包含源代码的演示、展示了如何使用此调试技术进入和退出 LPM4.5。 我没有找到这样的演示代码。 您能告诉我在哪里找到它(可能是汇编代码、而不是 c 代码)吗?

非常感谢。

Mauro