尊敬的团队:

一个奇怪的问题突然出现,我们不知道,你能在这里提供帮助吗?

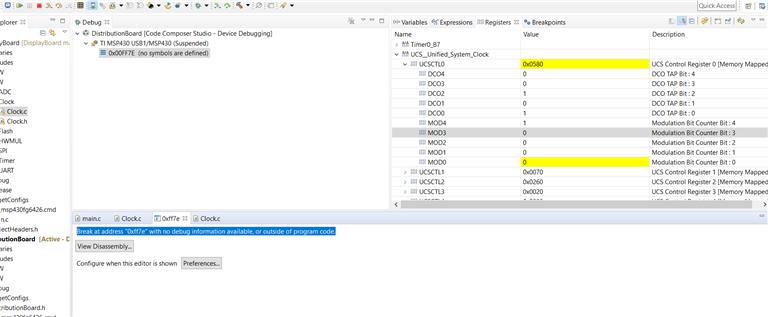

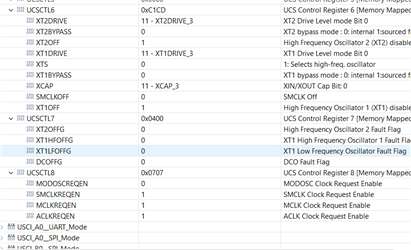

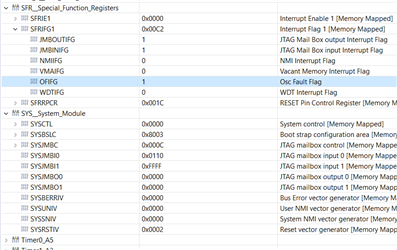

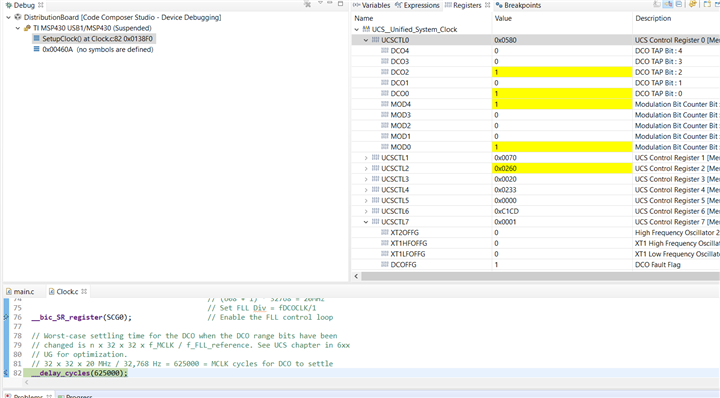

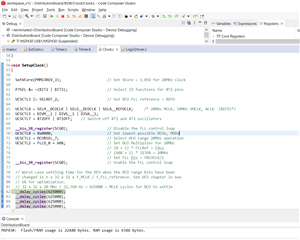

当我们在调试会话中刷写软件时、代码在第一次命中 _DELAY_CYCLES 之前运行良好、不会从这里继续。 每当我暂停执行时、断点就会停留在这里、不会继续。

但是、相同的代码运行良好、我的软件功能在没有调试会话的情况下与同一软件正常运行(只是停止了调试会话并点击了电路板上的复位按钮)。 在我们的某些器件中、相同的软件在发布模式下运行、没有任何问题。

我尝试重新创建一个新项目并导入源代码、调试会话在第一个实例中起作用、问题再次出现在第二个调试会话之后。 不确定哪里出现了问题、需要您的支持。

我在这里放置了代码以供参考

https://drive.google.com/file/d/1FmchPJjhVtBZjGTt-U79aiARngcFVcnF/view?usp=sharing

谢谢

Surya