您好!

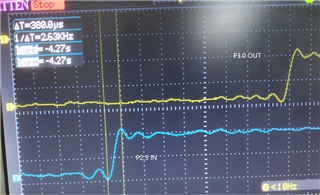

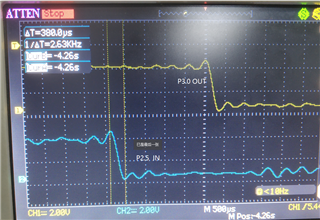

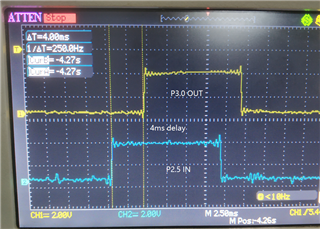

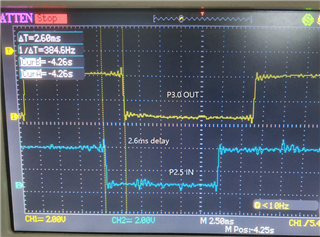

当输入 IO 信号发生变化时、我需要立即输出 IO 信号或 PWM。 。、发现响应延迟很严重、约为1.4-6ms μ s

简单。代码如下所示:

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P2DIR|=BIT5;

// P2REN&=~BIT5;

P2IES&=~BIT5;

P2OUT&=~BIT5;

P2IFG&=~BIT5;

P2DIR&=~BIT5;

//P2IE|=BIT5;

//p3.0 trigger out

P3DIR |= BIT0;

//P3REN|=BIT0;

while(1){

if(P2IN&BIT5) //p2.5: mcu-triggerIn

{

P3OUT|=BIT0;

}else{

P3OUT&=~BIT0;

}

}

}

或

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

//P2.5 interrupt

P2DIR|=BIT5;

// P2REN&=~BIT5;

P2IES&=~BIT5;

P2OUT&=~BIT5;

P2IFG&=~BIT5;

P2DIR&=~BIT5;

//P2IE|=BIT5;

//p3.0 trigger out

P3DIR |= BIT0;

//P3REN|=BIT0;

_EINT();

__low_power_mode_1();

}

//mcu-triggerin

#pragma vector=PORT2_VECTOR

__interrupt void Port_2(void)

{

P2IFG&=~(BIT5 | BIT4);

if(P2IN&BIT5) //p2.5: mcu-triggerIn

{

P3OUT|=BIT0;

P2IES|=BIT5;

}else{

P3OUT&=~BIT0;

P2IES&=~BIT5;

}

}

输入和输出端口的逻辑电平在外部进行监控、并找到延迟、延迟时间与输入电平的占空比和较长的等待时间有关。

我认为可能的原因是:

1) 1)外部输入电平发生变化、更新内部引脚寄存器的速度很慢

2) 2)从输出 IO 到驱动 IO 电平的变化很慢