工具/软件:Code Composer Studio

尊敬的团队:

请帮助 检查以下信息。 谢谢!

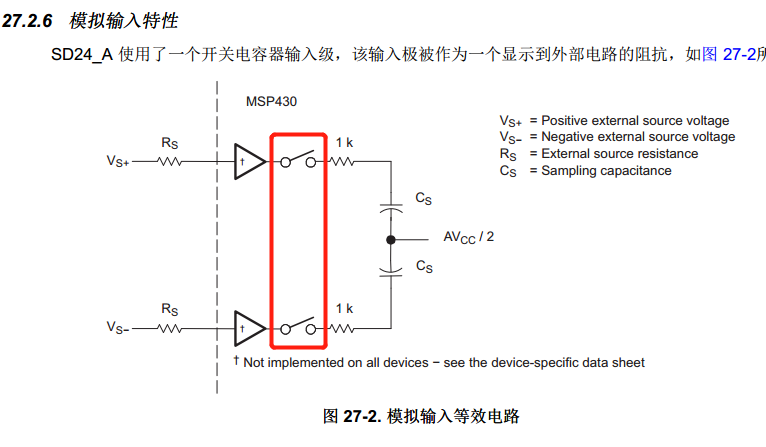

在芯片打开 ADC 以进行连续采样后、AD 通道输入的开关是否始终闭合?

如果它不总是闭合、那么每次生成 ADC 转换结果时、也就是下一次采样开始时、开关都会导通一次吗?

现在、ADC 的采样频率已调整为最高值、因为波形变化周期相对较快。 目的是尝试使采样波形不失真。 现在可以发现、在某些工作条件下、采样信号的相位正向偏移。 因此、请确认 AD 模块实际收集外部电压信号的时间点、以便排除故障。

电流采样电压变化不超过30mV、因此我认为这个滞后问题不应由 ADC 的阶跃响应引起。 我只能想到该开关对前端的影响

请帮助。