主题中讨论的其他器件:MSP430WARE、 MSP430F5438A、

您好!

我想在我上次离开的地方进一步讨论。 请查看我之前的帖子、该帖子几乎是9个月前的帖子。

https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/766491

现在、我在通信收发器和 MSP430之间使用 FPGA。

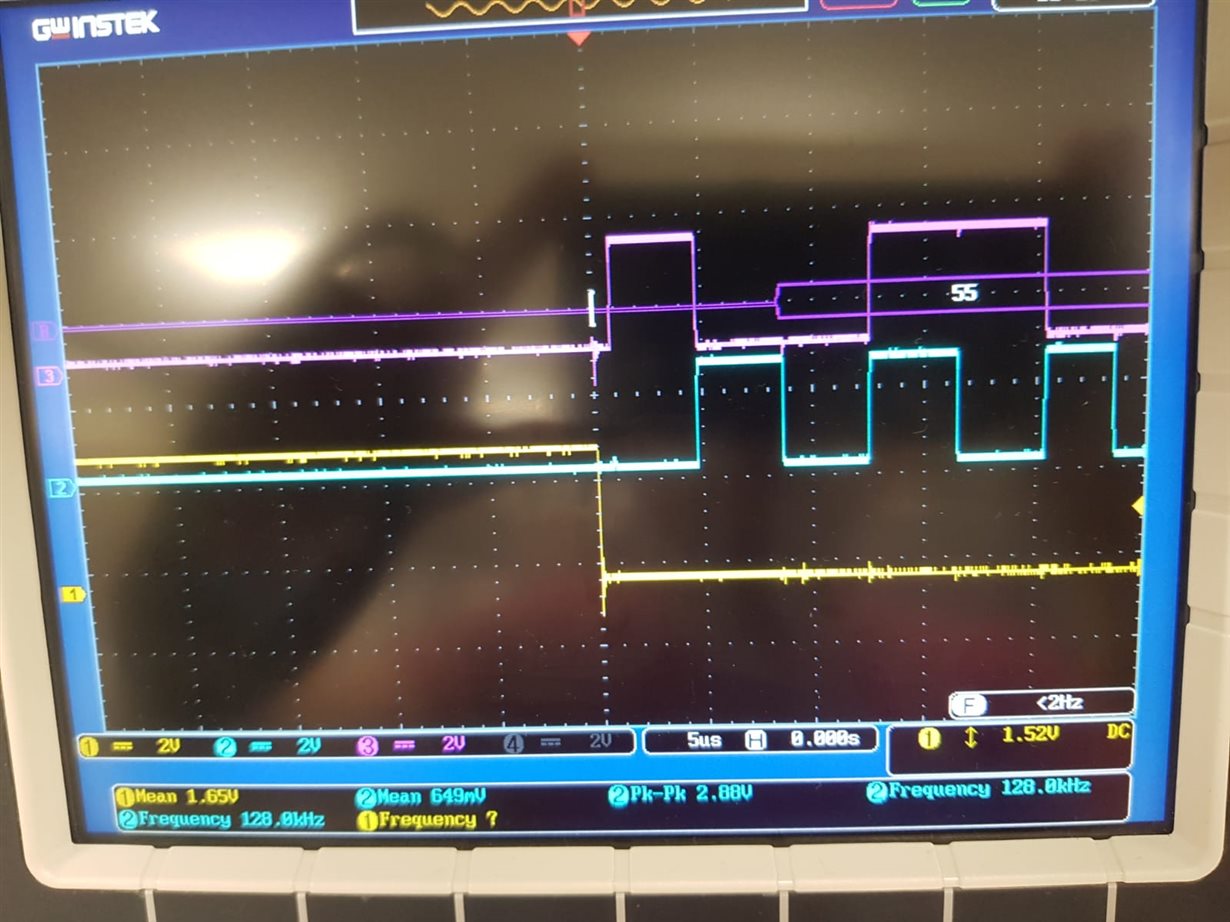

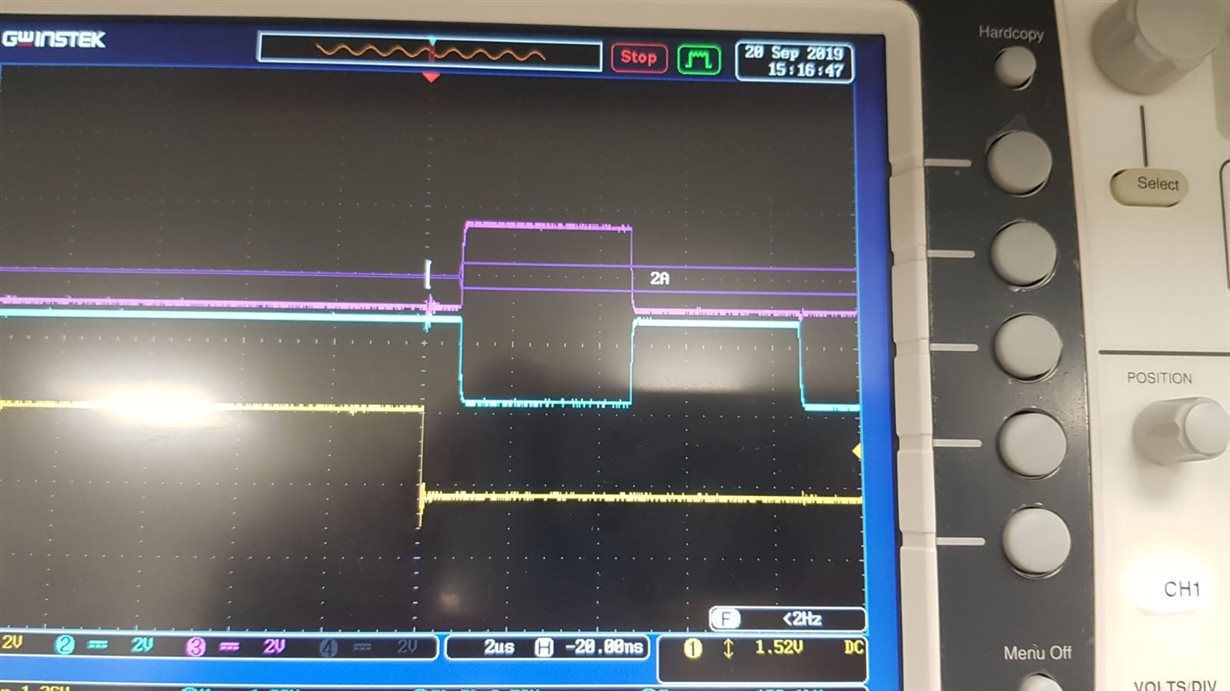

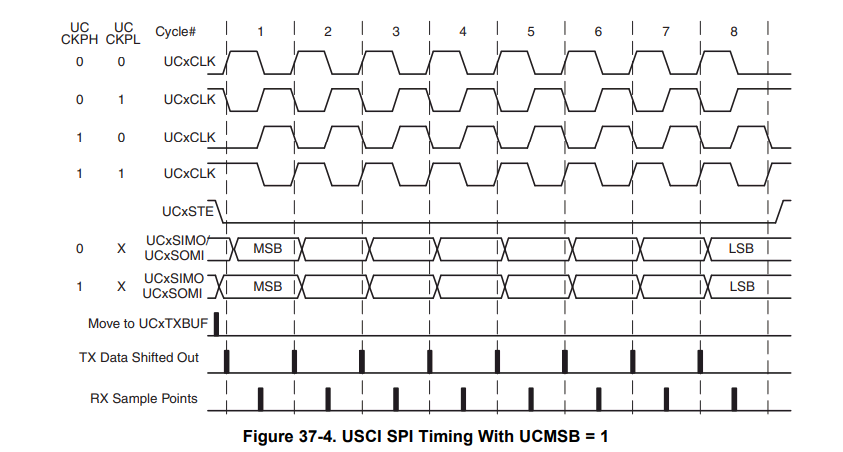

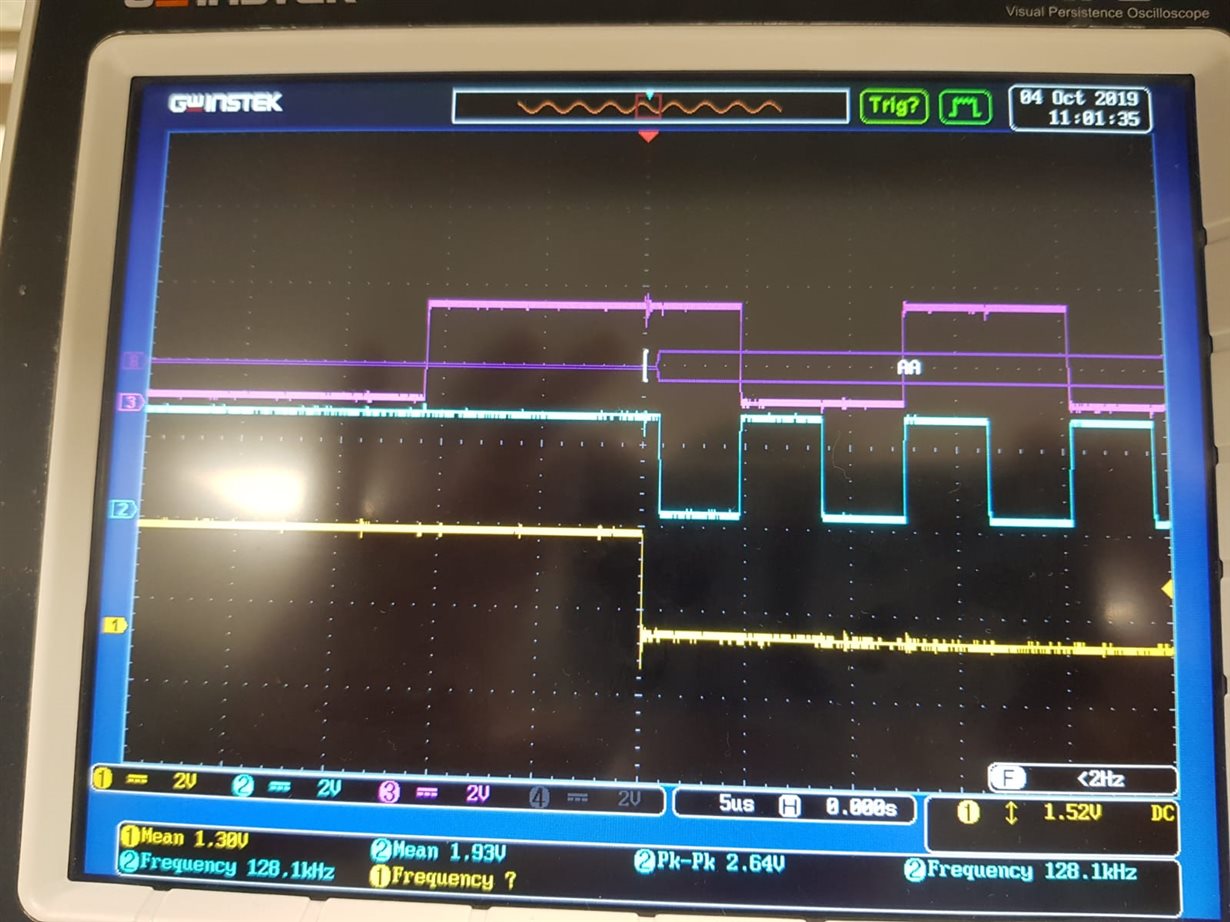

FPGA 将不断从通信收发器接收数据和 CLK、并查找在通信收发器提供的 CLK 上采样的数据模式。 我们称之为帧起始(SOF)的这种数据模式。 一旦它接收到 SOF、它将其引脚之一设置为片选(CS 高电平有效)为高电平、并将 CLK、数据和 CS 转发至 MSP430 SPI 从器件。 我们还有一个用于帧结束(EOF)的数据模式。 一旦 FPGA 看到 EOF、它将通过将 CS 设置为低电平来取消选择 MSP430 SPI 从器件。

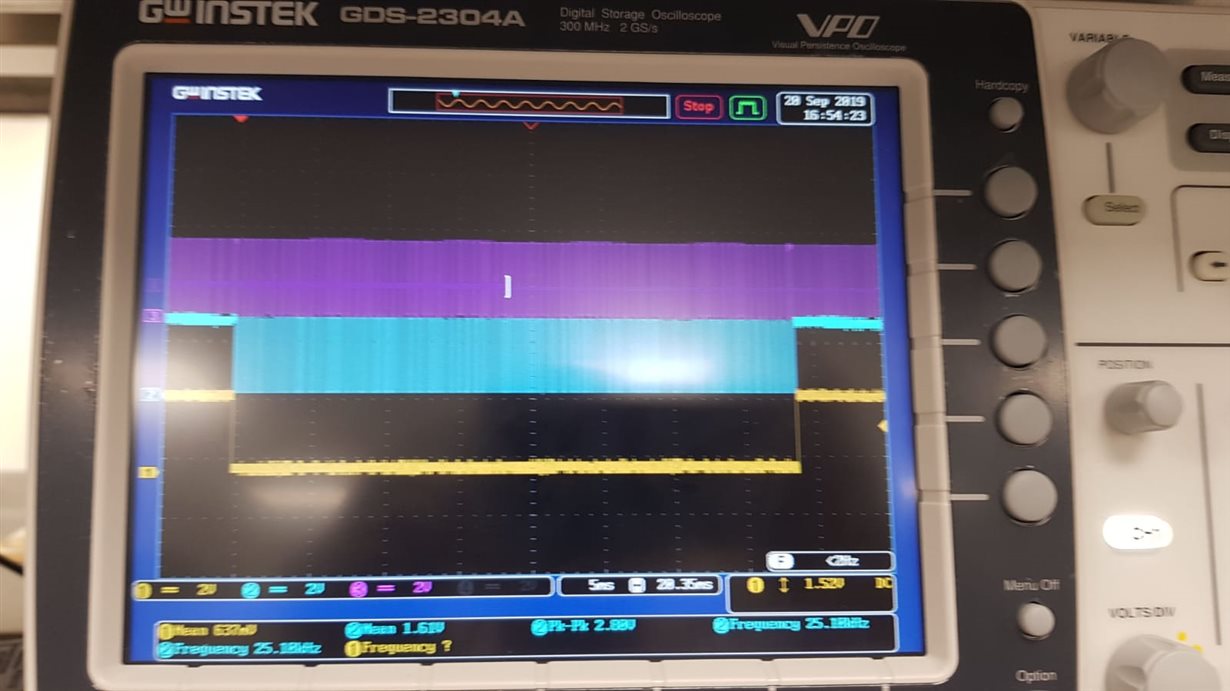

当我尝试运行我的系统并接收数据时、我的 MSP430有时会正确接收数据、有时会将数据移位几位(大约1-4位)。

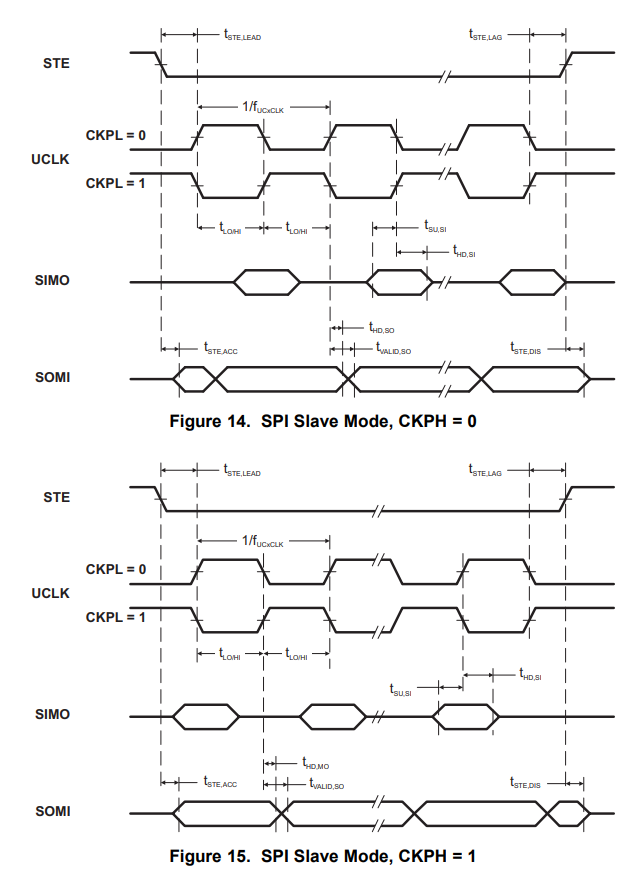

我意识到 CS 在 CLK 的同一边缘被激活、在该边缘将对数据进行采样。

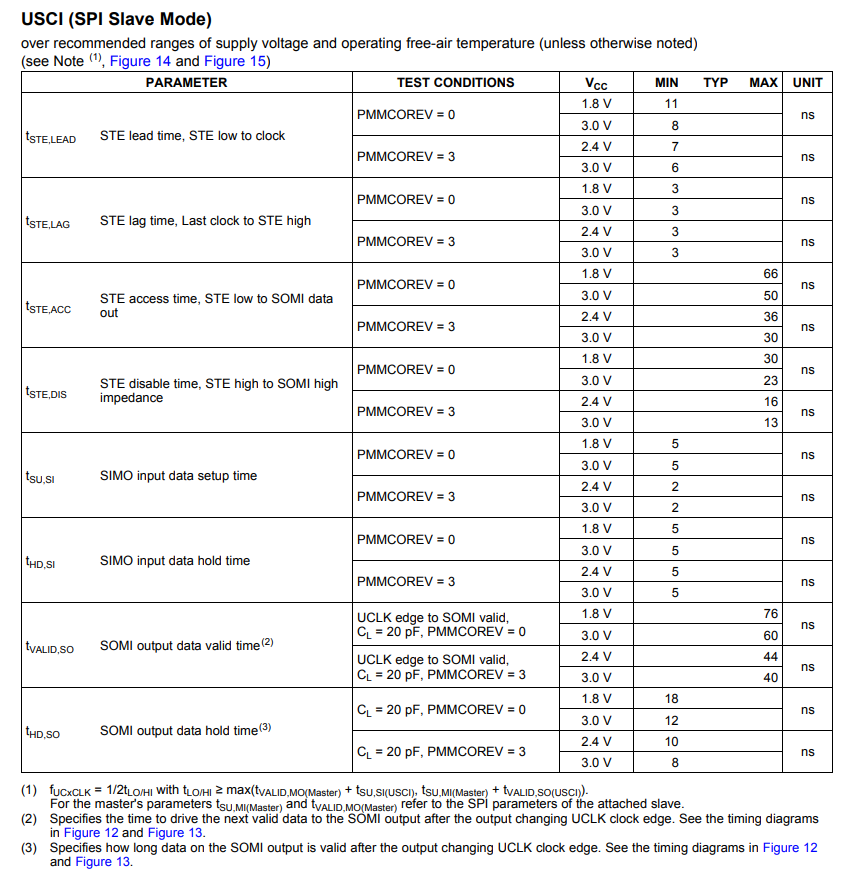

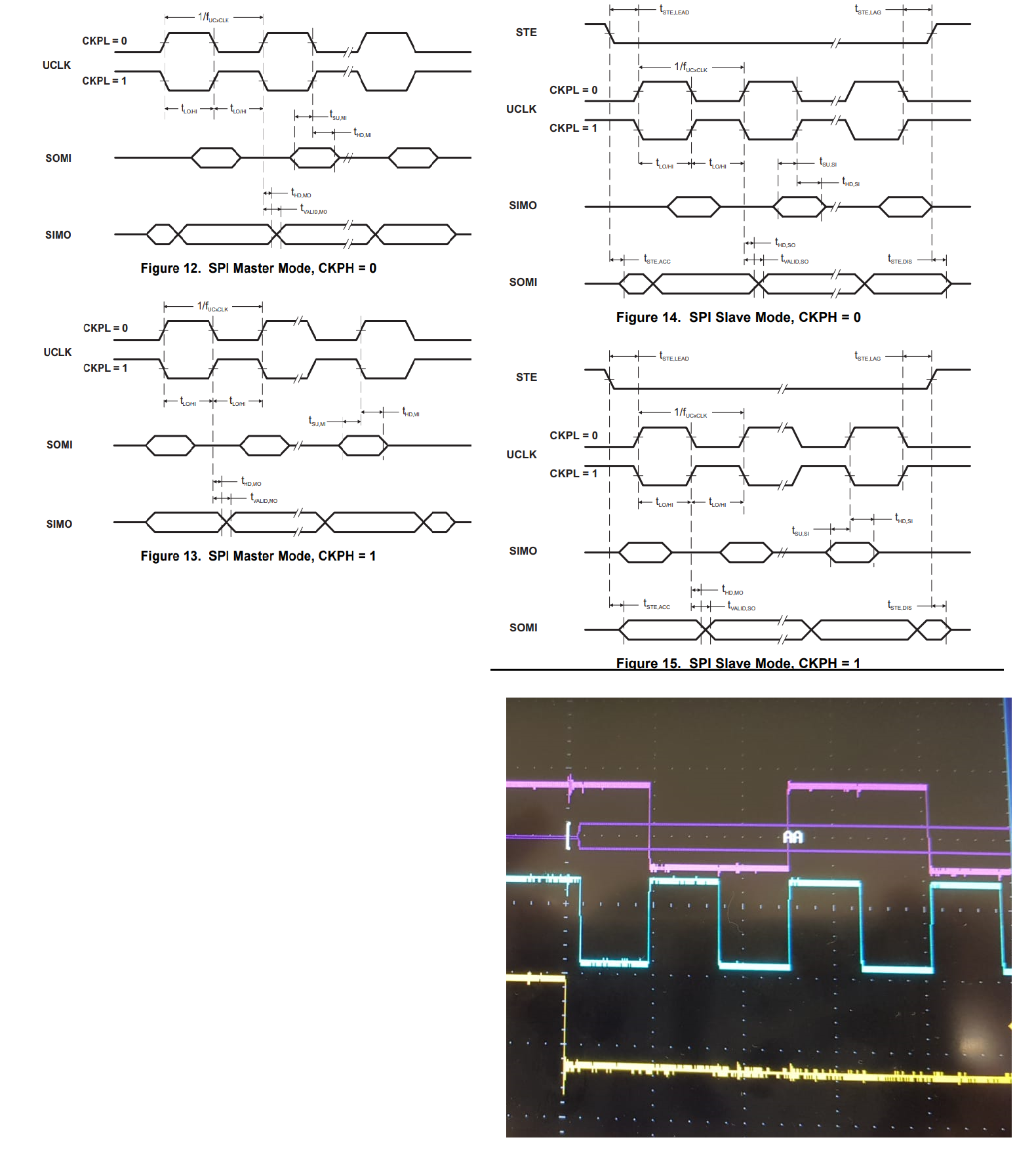

现在、似乎我正在使用 FPGA 创建自己的 SPI 主设备。 这意味着我需要处理如下所述的时序限制:

因此我的 CS 应该至少提前11ns。 我计划在下一个 CLK 和数据之前将 CS 置于 CLK/4时间附近的高电平。 没关系吗?

还有其他什么也会导致位移位问题吗? 另外、如果我还需要处理其他东西、请告诉我。

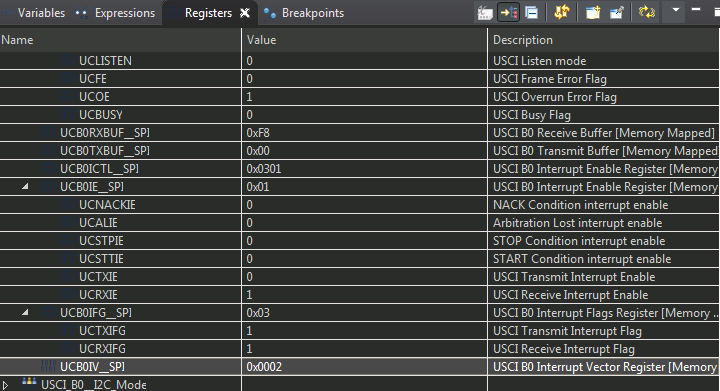

我想知道 SPI 从器件如何触发接收中断。 启用 SPI 后、它是否根据8输入 SPI CLK 触发?

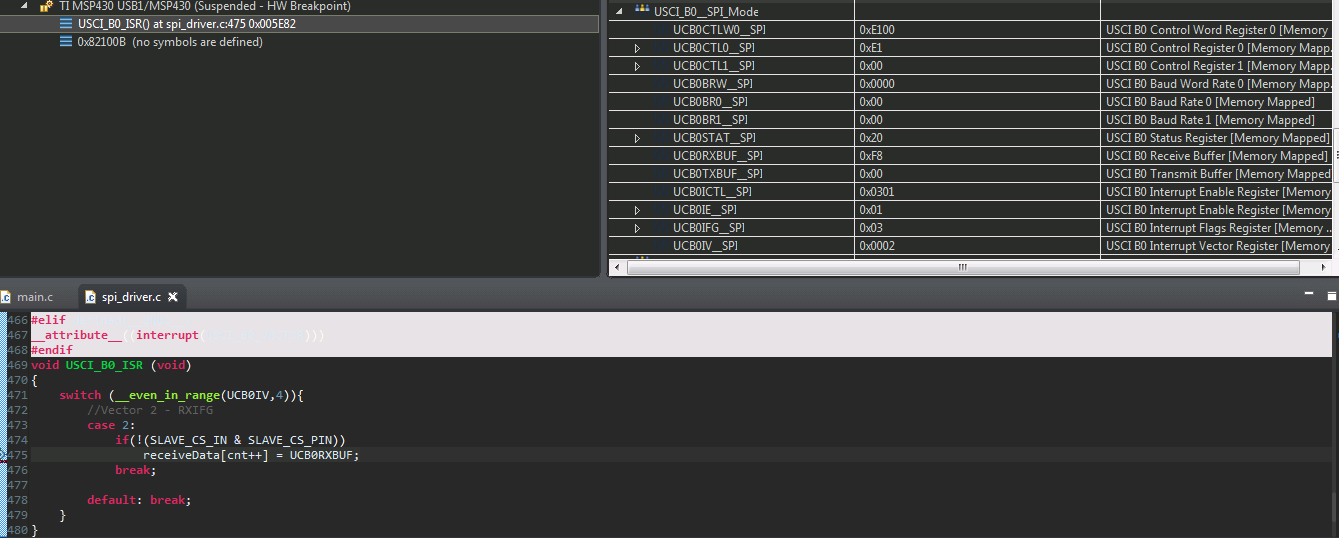

我的 ISR 如下所示(参考了来自 MSP430ware 的 SPI 从站 MSP430F5438A 示例):

#define SLAVE_CS_IN P3IN

#define SLAVE_CS_DIR P3DIR

#define SLAVE_CS_PIN BIT0

空 USCI_B0_ISR (空)

{

开关(_偶数_在范围内(UCB0IV、4)){

//Vector 2 - RXIFG

案例2:

IF (SLAVE_CS_IN 和 SLAVE_CS_PIN)

receiveData[cnt++]= UCB0RXBUF;

中断;

默认值:break;

}

}

谢谢、此致、

Ankit