处理器: MSP430F5172

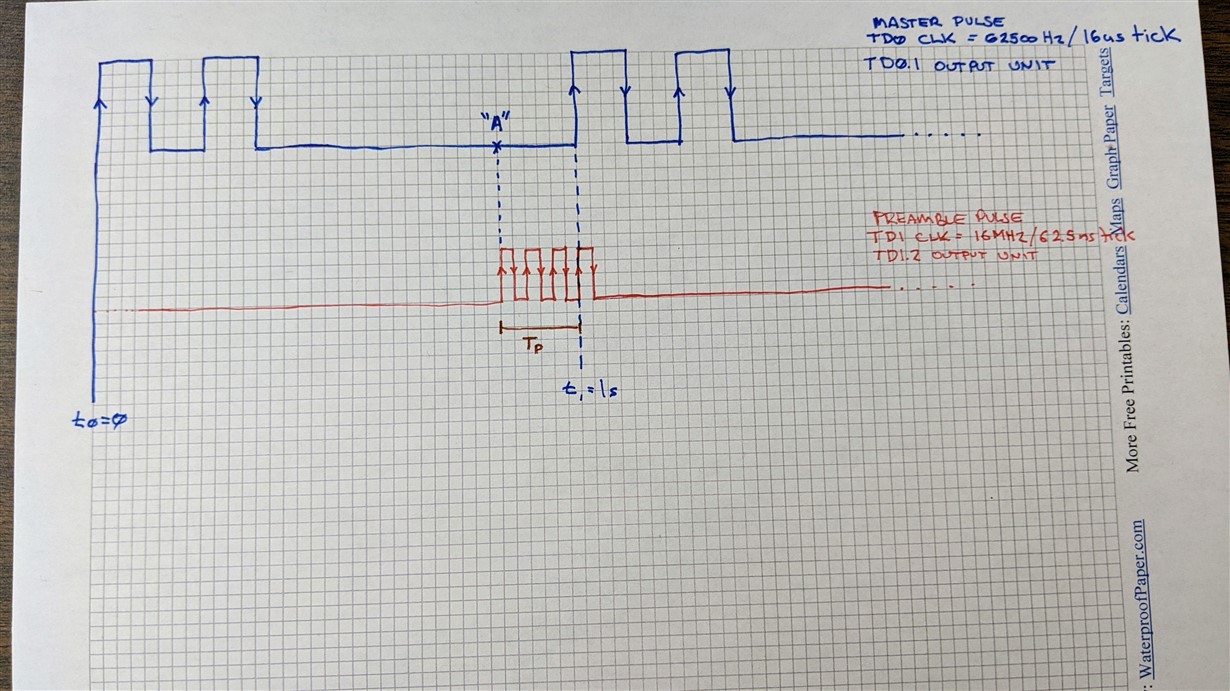

我想知道、当两个不同定时器的时基不同时、在两个 CCR 输出模块之间实现上升沿同步的最准确方法是什么。 理想情况下、我希望边沿在彼此之间的几个 MCLK 内发生、最好小于10。 请记住、这个帖子 是整个项目的总体简化、但它具有一个基本概念。 首先、让我用图表进行演示:

顶部脉冲序列由 TD0和 TD0CCR1生成、其输出比较单元配置为在引脚 TD0.1上输出 TD0、配置为使用通过常用时钟分频器生成的62500kHz 时钟运行。 脉冲序列本身有一个1秒的周期; 因此、在这个脉冲序列的任何一个周期内、总共发生62500个 TD0时钟周期。 脉冲序列时序由(1)一个数组生成、该数组保存间隔(2)保存要知道何时处于图形末尾的边沿数的常量(3)时序数组中位置的索引、以及(4) 保存的变量 电流脉冲状态为高电平或低电平(5) ISR 会递增要定时的间隔并修改 TD0CCR1

下面是我的一些示例代码、展示了如何生成顶部脉冲序列:

#include

#include

// //

//输出脉冲时序

// ACLK @ 500kHz * 1/8分频器= 16us/tick

//

//注意:针对连续模式的 TD0/TD1置1

// pulseTiming_master[]乘以交替高电平周期、低电平周期、高电平周期、低电平周期等

////

注:此数组中的所有元素都应加1 / 16us =62500

// //

// 75ms 接通、100ms 关断、75ms 接通、700ms 关断

uint16_t pulseTiming_master[4] ={4688、6250、4688、46874};

常量 uint8_t numEdges_master = 4;

volatile uint8_t pulseIdx_master = 0;

易失性 pulseState_t curPulseVal_master =低电平;

//此 ISR 在 TD0R 计数到 TD0CCR1-6时触发

// OUTMOD_1 -->设置硬件输出单元中的引脚

// OUTMOD_5 -->重置硬件输出单元中的引脚

// PJ.6 --> TD0.1 --> PULSE

#pragma Vector = TIMER0_D1_VECTOR

__INTERRUPT void Timer0_D1_ISR (void)

{

switch (TD0IV)

{

情况0: //无中断;为 CCR0保留

中断;

案例2: // TD0CCR1

if (curPulseVal_master ==低电平) //... 引脚翻转为高电平、然后我们进入该 ISR ...

{

//引脚现在设置为高电平、下一个中断要将其复位为低电平

TD0CCTL1 = OUTMOD_5 | CCIE;

curPulseVal_master =高电平;

}

其他

if (curPulseVal_master ==高电平) //... 引脚翻转为低电平、然后进入该 ISR ...

{

//引脚现在复位为低电平、下一个中断需要将其设置为高电平

TD0CCTL1 = OUTMOD_1 | CCIE;

curPulseVal_master =低电平;

}

//更新时间间隔

TD0CCR1 = TD0R + pulseTiming_master[pulseIdx_master];

//更新脉冲时序数组的索引...

if (pulseIdx_master < numEdges_master - 1) pulseIdx_master++;

其他 pulseIdx_master = 0;

中断;

案例4: // TD0CCR2

中断;

默认值:__never_executed();

}

}

int main (void)

{

WDTCTL = WDTPW | WDTHOLD;//停止看门狗计时器

//假设时钟系统已经配置了 MCLK = 16MHz、ACLK = 500kHz…… 此处未显示此内容

//停止计时器和清除分频器

TD0CTL0 = TDCLR;

TD0R = 0;

// TD0使用 ACLK @ 500kHz (2us)作为输入时钟;输入分频器= 8;连续模式;16位;独立组;

TD0CTL0 = TDSSEL_ACLK | ID_8 | CNTL__16 | SHR_0 | TDCLGRP_0;

//扩展 div = 1.

TD0CTL1 = TDIDEX__1;

//确保脉冲时序从初始条件开始

pulseIdx_master = 0;

curPulseVal_master =低电平;

//当 TD0R"计数到"TD0CCR1时、输出信号受到影响

TD0R = 0xFFFF;

TD0CCR1 = 0;

//立即加载;以设置操作的形式启动输出;启用中断

TD0CCTL1 = CLLD_0 | OUTMOD_1 | CCIE;

//开始计时器运行

TD0CTL0 |= MC__Continuous;

_bis_SR_register (GIE); //启用全局中断

while (1)

{

}

返回0;

}

好的,所以总体想法(参考图示)是为主脉冲的第一个上升沿(用蓝色图示)提供某种前导码 (用红色图示)。 包含第一个主器件上升沿之前的任意数量的脉冲(这些脉冲将在高/低时间以及数量的最终应用中发生变化) 前导码的最后一个上升沿必须同时发生、 或非常接近主脉冲的上升沿。

与此相关的是、该前导码脉冲由不同的计时器 TD1运行、并且 TD1的时钟频率为16MHz。 这个脉冲在 TD1的控制下、使用 TD1CCR2输出单元、在 图中的 TD1.2引脚上输出脉冲、我可以进行一些时间数学运算来确定点"A"的位置、但我不知道在出现"A"时在软件中该怎么办。 此外、我不确定如何处理 TD0R 翻转和 TD1R 翻转之间的较长时间差。 实际上,前导码脉冲的高/低时间大约 为32 - 128us ... 需要将这个16MHz 输入时钟连接到 TD1。

从 TD1生成此前导码的方法与主脉冲相同或相似、即使用输出比较单元、然后在 ISR 中读取线性数组中的值、为下一个间隔计时、直到达到前导码模式的末尾。 从这个意义上讲、前导码本身的周期等于主器件的周期; 在这里的简单示例中、1秒。

在 MSP430论坛上与所有计时器专家联系: 如果您必须实现我在上面所述的目标、您将如何实现? 是否有办法使主器件/前导码脉冲的边沿精确对齐? 如果不是、我将在软件中执行什么操作来实现此帖子中所述的近距离同步?