尊敬的 TI 团队:

我们正在开发基于 TI CC430F6137的产品。 下面是器件初始化例程的快照、该例程启用了32.768kHz 时钟晶体提供的 XT1 CLK。 此外、XT1_CLK 用作 PLL/DCO 的参考信号并生成 MCLK。

在单步执行初始化例程的过程中,我们偶尔会遇到一种情况,即 MCU 被困在 do-while 循环中(粗体),因为 DCOFFG 标志 总是设置为1,而不管它在循环中被清除。 当我们在角色中快速打开/关闭 CC430F6137电源多次时、这种情况会偶尔发生一次。 一旦器件进入此状态、通过系统复位引脚复位器件不会有所帮助、因为 MCU 会一直被捕获在 while 环路中。 解决此问题的唯一方法是以正常方式回收 MCU 的电源。 您是否会查看我们的初始化代码、并为我们提供建议、以帮助我们解决遇到的问题? 谢谢你。

此致、

Peter

MCU 时钟初始化例程

{

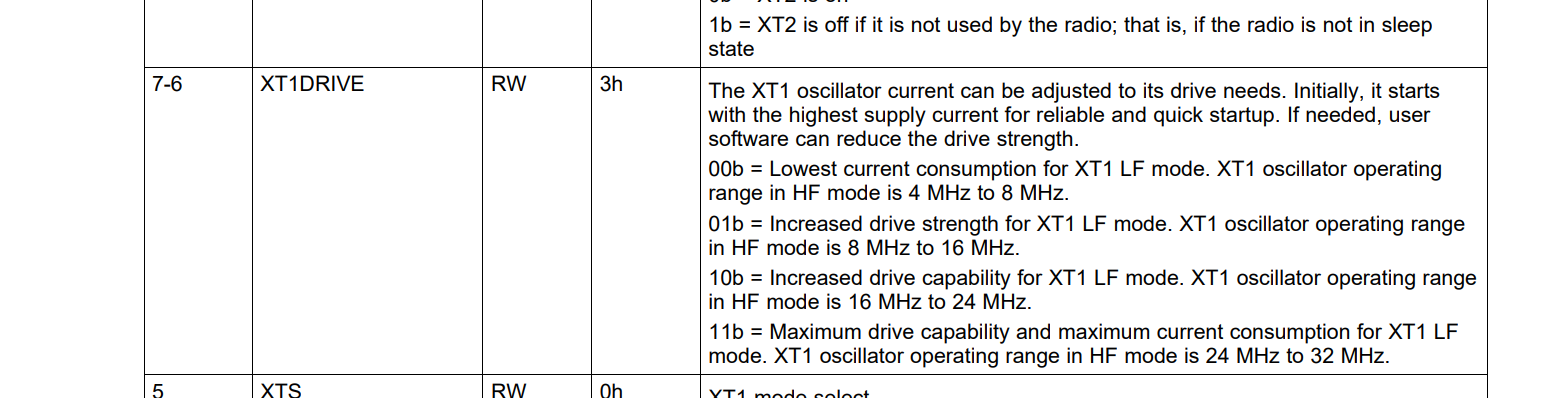

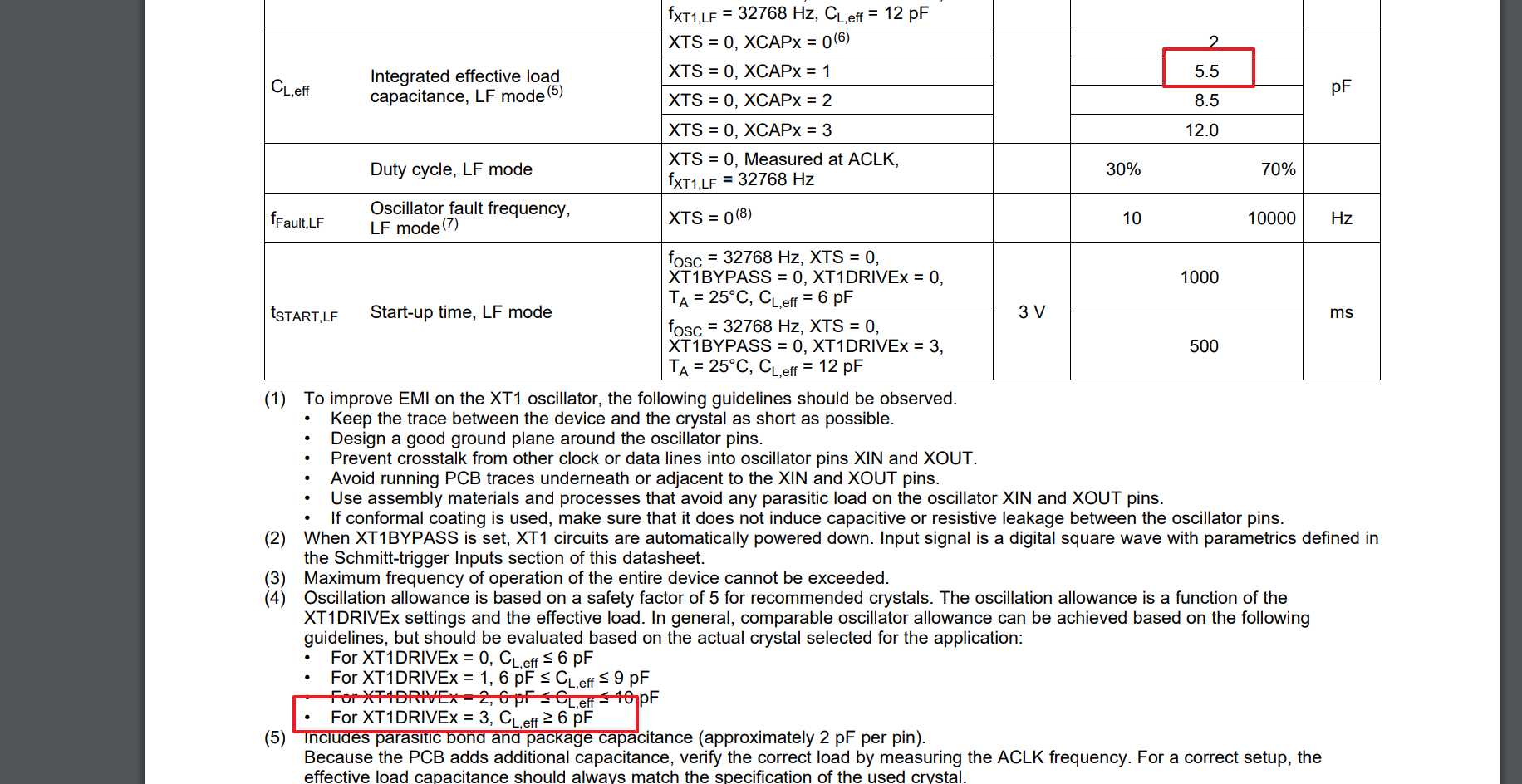

UCSCTL6 &=~XCAP_3; //清除 XCAP 值

UCSCTL6 |= XCAP_1; //将 XCAP 值设置为6pf

P5SEL |=(BIT0 | BIT1); /*为 XT1的外部源设置 P5.0和 P5.1 */

_DELAY_CYCLES (375000);

UCSCTL3 &=~SELREF_7; /*设置 DCO FLL 基准= XT1 */

UCSCTL4 |= SE拉美 经济体系2; /*设置 ACLK = REFO */

_bis_SR_register (SCG0); /*禁用 FLL 控制环路*/

UCSCTL0 = 0x0000; //设置尽可能低的 DCOx、MODx *

UCSCTL1 = DCORSEL_5; /*选择 DCO 范围24MHz 操作*/

UCSCTL2 = FLLD_1 + 499; /*(499 + 1)* 32768 = 16384000Hz */

_BIC_SR_register (SCG0); /*启用 FLL 控制环路*/

/* DCO 范围位已经过的最差情况下的稳定时间

*已更改 n x 32 x 32 x f_MCLK / f_FLL_reference。

* 32 x 32 x 16 MHz/32、768Hz = 500000 = DCO 稳定的 MCLK 周期

*

_DELAY_CYCLES (50000); /*延迟周期根据公式*/更新

/*循环直到 XT1、XT2和 DCO 故障标志被清除*/

操作

{

UCSCTL7 &=~(XT2OFFG + XT1LFOFFG + DCOFFG) /*清除 XT2、XT1、DCO 故障标志*

SFRIFG1 &=~OFIFG; /*清除故障标志*/

} while (SFRIFG1&OFIFG); /*测试振荡器故障标志*/

}