我遇到了较长的 CTSD16转换时间问题。

请告诉我原因。

CTSD 的主要设置如下。

采样率= 32个时钟

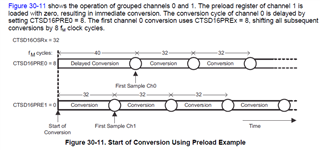

PreloadValue=0时钟

CTSD16INTDLY=1b (第一个采样引起中断)

CTSD16RRI=1b (轨到轨输入被启用)

连续转换模式

SMCLK=4MHz

转换结果由 DMA 存储在缓冲存储器中。

在转换指定次数后、CTSD 转换由 DMA 中断停止。

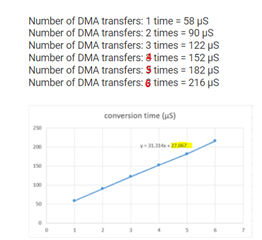

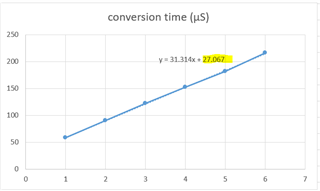

从 CTSD 转换开始到由 DMA 中断停止 CTSD 转换的时间如下所示。

μS 传输数量:1次= 58 μ s

μS 传输数量:2次= 90 μ s

μS 传输数量:3次= 122 μ s

μS 传输数量:3次= 152 μ s

μS 传输数量:3次= 182 μ s

μS 传输数量:3次= 216 μ s

垂直轴表示转换时间、水平轴表示 DMA 传输的数量。

所有转换时间都增加了大约27µS μ s。

您认为添加此27μS 的原因是什么?