主题中讨论的其他器件:MSPDRIVERLIB

大家好!

我需要有关配置 PMM 模块以在最高 VCORE 电压下运行的帮助、以便在24MHz 下运行器件。

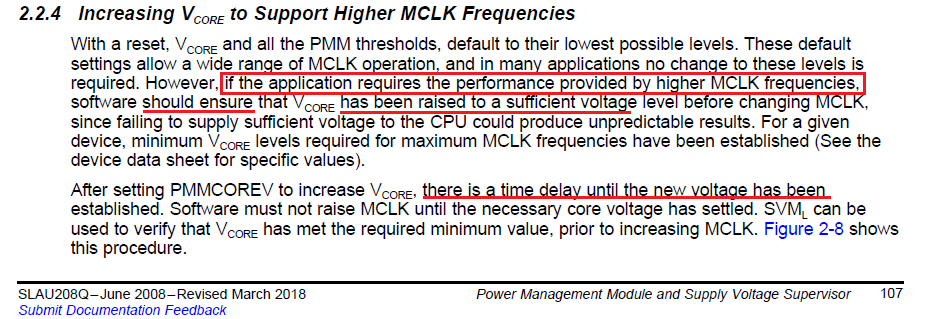

如用户手册的相关章节所述、 VCORE 电压需要以单个增量步长增加、而不是以一个大步长增加到最终电平、如下所示:

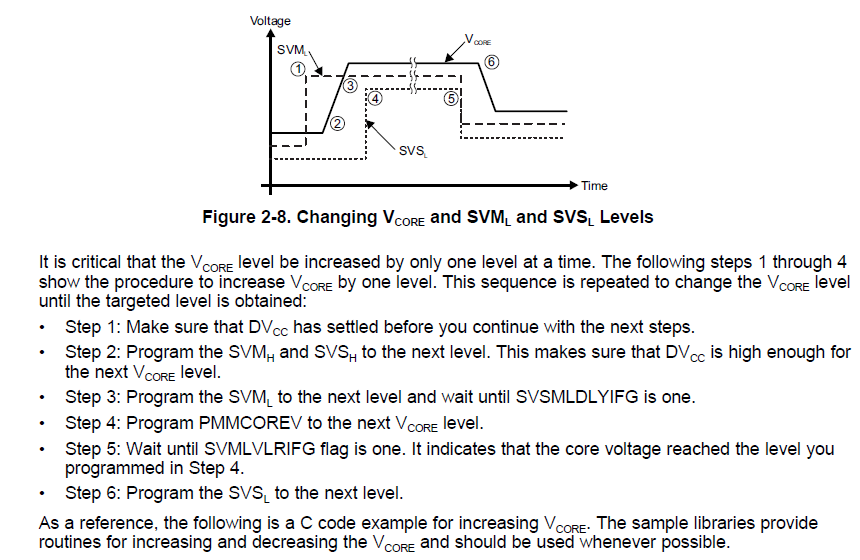

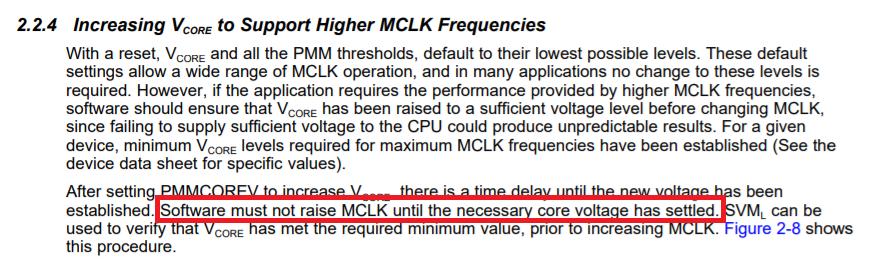

此外、用户手册 SLAU208Q 在第108页中概述了以下步骤:

在另一个参考中、数据表提到频率也应逐步增加、以达到最终目标工作频率。

将这两者结合起来、我使用 for 循环来将 Vcore 电平增加一步、频率串联起来也是如此。

我的第一个问题是-这是否正常? 或者、我是否应该让 Vcore 电压达到其所需的电平、然后单独增加频率?

我的第二个问题:执行会卡在 SET_Vcore 函数内的第一个 while 循环中,如下所示。

我的代码如下所示。

void set_vcore (unsigned int level) { level &= 0x0007;//限制电平获取非法值 PMMCTL0_H = PMMPW_H;//在 (!(PMMIFG & SVSMHDLYIFG))时打开 PMM 寄存器进行写入访问;//代码卡在此处!! 永远不会把 SVSMHDLYIFG 的标志拉高!!! while (!(PMMIFG & SVSMLDLYIFG)); SVSMHCTL = SVSHE + SVSHRVL0 *电平+ SVMHE \ +(SVSMHRRL0 *(电平+ 1));//将 SVS/SVM 高侧设置为新电平 SVSMLCTL = SVSMLE + SVMLE + SVSMLRL0 *(电平) ;//将 SVSMLPMSMLPM0设置为新电平!//等待 SVM 稳定 PMMIFG &=~(SVMLVLRIFG + SVMLIFG);//清除已设置的标志 PMMCTL0_L =(电平& 0x03);//如果 ((PMMIFG & SVMLIFG))将 VCORE 设置为新电平 //等待直到达到新电平(!(PMMIFG & SVMLIFG); SVSMLCTL = SVSLE + SVSLRVL0 *电平+ SVMLE \ +(SVSMLRRL0 *(电平+ 1));//将 SVS/SVM 低侧设置为新电平 PMMCTL0_H = 0x00;//锁定 PMM 寄存器以进行写入访问 }

此函数从 main 中调用、如下所示:

int main (void) { ///---------------------------------------------------------- //开始初始化序列 ///---------------------------------------------------------- WDTCTL = WDTPW | WDTHOLD;//停止看门狗计时器 __ bis_SR_register (SCG0);//禁用 FLL 控制环路 UCSCTL6 |= XT1BYPASS;//旁路振荡器、简化驱动 UCSCTL1 = DCORSEL_2;//选择最低 DCO 范围 UCSCTL3 = SELREF_0;//设置 DCO FLL 基准= XT1CLK/1 UCSCTL4 = SELA_REFOCLK \ + SELM_REFOCLK;//设置 ACLK = REFO for WD (独立) UCSCTL0 = DCO2 + MOD2;//设置中等 DCOx、MODx UCSCTL2 = FLLD_0;//将 DCO 乘法器设置为最低频率 //(N + 1)* FLLRef = Fdco //(487 + 1)* 32768 = 16MHz __DELAY_CYCLS (10000);//振荡器稳定 FLL_Step_Incrmt 的稳定延迟();//在步骤 __DELAY_CYCLLES (1000)中将时钟设为目标频率;//振荡器稳定 __BIC_SR_register (SCG0)的稳定延迟;//启用 FLL 控制环路 // DCO 范围位已 更改 n x 32 x 32 x f_MCLL_f 参考时最坏情况下的稳定时间。 有关优化、请参阅5xx // UG 中的 UCS 一章。 // 32 x 32 x 16 MHz / 32、768Hz = 500000 = MCLK 周期、DCO 稳定 //循环、直到 XT1、XT2和 DCO 故障标志被清除 DO { UCSCTL7 &&=~(XT2OFFG + XT1LFOFFG + DCOFFG);//清除 XT2、XT1、DIFG、DIFG 和 = RFIFG;//清除 XT2 FAULT1 =~ //清除故障标志 } while (SFRIFG1 & OFIFG);

其中 FLL_StepIncrement 如下所示:

void FLL_Step_Incrmt (void)

{

unsigned int i;

unsigned int dcorval = 0x0020;

for (i=1;i<4;i++)

{

SET_Vcore (I);

UCSCTL1 = dcorval + 0x0010;

_DELAY_CYCLES (256);//

}

}

代码在第一个 while 循环中停留在设置 Vcore 函数的循环中。 我缺少什么吗? 我是否需要启用延迟中断标志?

如果有任何帮助,将不胜感激。 谢谢

此致

Aniruddha