团队、

我们在 MSP430FR6922的叉形晶体方面存在问题。 我们需要为 MCLK 设置8MHz 并将外部晶体设置为 ACLK。

下面您可以看到我们使用的函数、如果我们使用该函数、MSP430FR6922会保持循环 DO -而持续几秒钟。 该时间是随机的、介于1秒和无穷大之间。

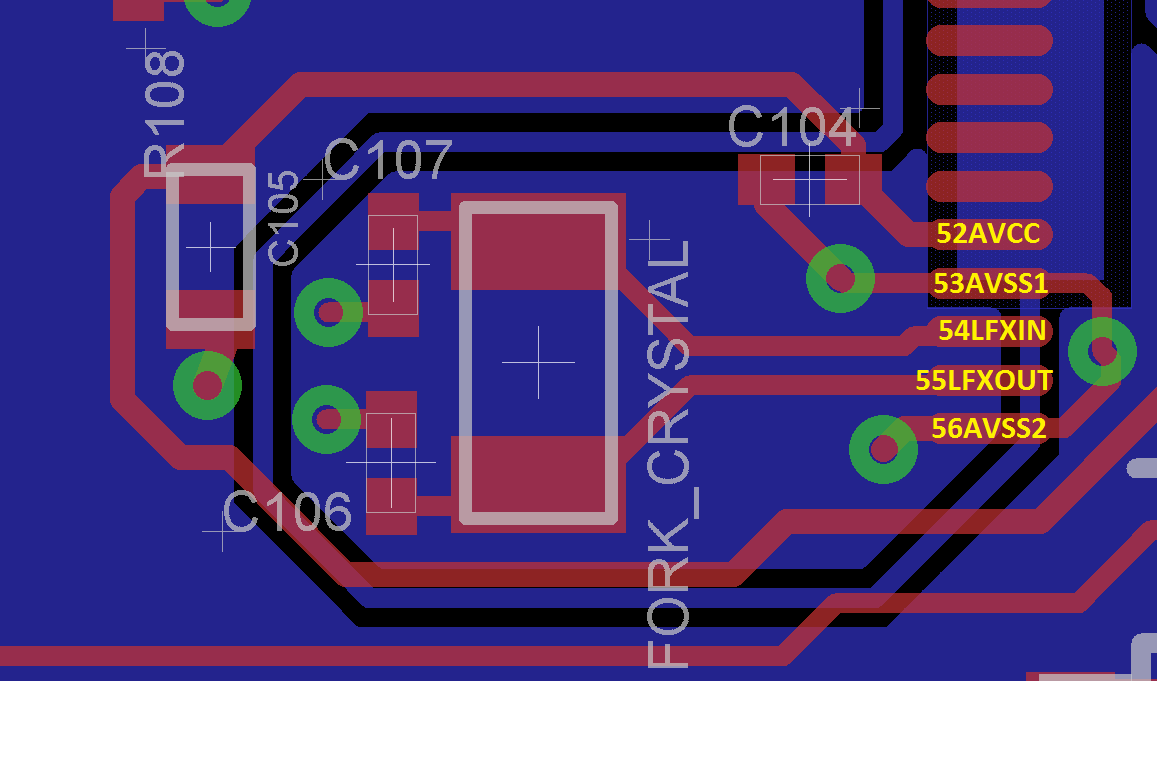

晶体参数为:

- 封装:3215

- 负载电容:6pF

- 频率:32768Hz

您能不能告知问题是什么、或者代码中的错误是什么?

需要注意的一点是、如果我们在 JTAG 编程器上使用 msp430fr6922、则不会发生所描述的问题。 如果我们拔下此插头并连接到3V 电源、则说明的问题将开始。

感谢你的帮助。

TI 客户

void ClocksStart (void) { PJSEL0 |= BIT4 | BIT5; //为晶振启用时钟功能引脚。 //禁用 GPIO 上电默认高阻抗模式以激活 //先前配置的端口设置 PM5CTL0 &=~LOCKLPM5; SFRIE1~……OFIE;//阻止发生晶体错误时发生的中断 //设置时钟 CSCTL0_H = CSKEY >> 8; //解锁 CS 寄存器 CSCTL1 = DCOFSEL_6; // DCORSEL = 0A DCOFSEL=6 (DCOFSEL=110)->8MHz CSCTL4 &=~ LFXTDRIVE_2; //设置晶振的功率、LFXTDRIVE 00 - 3、5pF、LFXTDRIVE 01 - 6pF、LFXTDRIVE 10 - 9pF、LFXTDRIVE 11 - 12pF CSCTL2 = SELA_LFXTCLK | SELESS__DCOCLK | SELM_DCOCLK;//设置 ACLK = XT1;MCLK = DCO CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; //将所有分频器设置为1 CSCTL4 &=~LFXTOFF; //启用晶振。 P9DIR |= BIT5; 操作 { P9OUT ^= BIT5; CSCTL5 &=~LFXTOFFG; //清除 XT1故障标志 SFRIFG1 &=~OFIFG; } while (SFRIFG1和 OFIFG); //测试振荡器故障标志 CSCTL0_H = 0; //锁定 CS 寄存器 SFRIE1 |= OFIE; //允许发生晶体错误时发生的中断}