您好!

我们在批量生产的项目中使用了 MSP430FR5738 uC。 现在、我们收到了一些客户抱怨功能错误的反馈。 在实验练习中进行调试后、我们找到了问题的根源。

我们在 P2.2上使用 ISR 进行下降沿检测。 下面列出了引脚初始化。

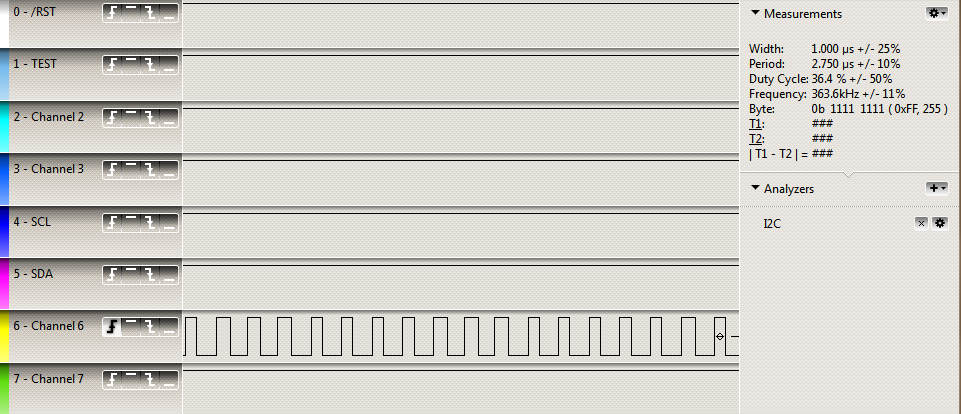

当我们对线路进行示波时、电压保持在3.3V、并且 P2.2的输入端没有真正的持续操作(示波器上的触发电平为~2V)。 而这种情况下、UC 会始终跳转到 ISR。 我会说在1500个器件中的1个器件上发生了这种情况。 我们可以认为这可能是 ESD 损坏、但这条线路仅用于内部 AN、没有连接到某些外部引脚。 你有什么想法吗?

此致

//main.c P2DIR = 0x00; P2OUT = 0x00; void init_p22 (void){ P2IFG &=~BIT2; P2OUT |= BIT2; P2IES |= BIT2; P2REN |= BIT2; P2IE |= BIT2; } #pragma vector=port2_vector __interrupt void P2_ISR (void) { if (P2IFG && BIT2)// P2.2中断? { //此处的一些操作 } P2IFG = 0x00;//删除所有 IR 标志 }