主题中讨论的其他器件:SN75C185、

我有一位客户希望使用连接 到 MSP430F5418A 的 SN75C185。

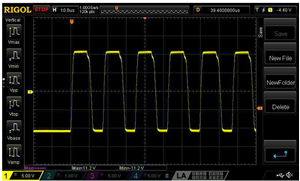

但是、他们意识到 SN75C185 -> MSP430的输出波形、更具体地说、高/低位长度是不同的。

当波特率为115.2kbit/s 时、每个位周期的周期为~8.7us。

但高电平时间大约为1.2us "太长"、而低电平时间大约为1.2us "太短"。

对于异步 UART 通信、我对此主题不太清楚、但 MSP430会对位流进行多次采样、并获取大部分采样点?

为了使此类波形能够正常工作、需要满足哪些条件才能与此 MSP430器件正常工作?

我们非常感谢您提供任何建议/帮助。

此致、

Darren