配置:

UCB0CTL1 |= UCSWRST;

P1SEL |= SIMO + SOMI + CLK;

P1SEL2 |= SIMO + SOMI + CLK;

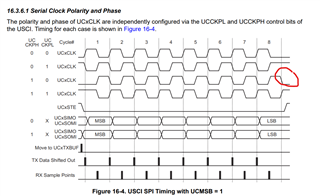

UCB0CTL0 = UCMST;//主模式选择

UCB0CTL0 |= UCSYNC;//同步模式

UCB0CTL0 |= UCMSB;//MSB FIRS

UCB0CTL0 |= UCCKPH;//时钟相位非活动状态为低电平

//UCB0CTL0 |= UCCKPL;//未激活状态为高电平

UCB0CTL1 |= UCSSEL_3;//10b = SMCLK

UCB0BR0=16;//低字节

UCB0BR1 = 0;//高字节

IFG2 &=~UCB0TXIFG;

IFG2 &=~UCB0RXIFG;

UCB0CTL1 &=~μ H UCSWRST;

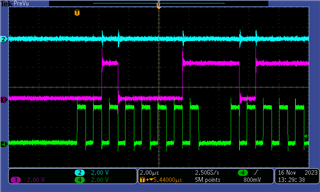

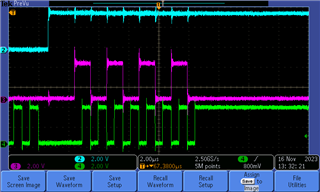

绿色 CLK

蓝色 -诺基亚5110显示屏的数据/代码

紫色 是数据

tek00418.png 是第一个字节

tek00425.png 是最后一个字节

如果保持高电平并且不考虑最后8个字节有效、则不考虑第8位的 Nokia 5110时钟问题。

如果我再次写入8位验证前8位将考虑,但不是当前最后8位 .

传输 :第一个字节(不考虑任何显示的内容);第二个字节(出现在5110第一个数据字节);第三个 字节(出现在5110第二个数据字节)...

如果我为 CLK (端口1位5)设置制动点并复位 CIP 选择、CLK 将变为低电平并在显示屏上显示最后字节数据。

您能提出任何解决方案吗?

谢谢