主题中讨论的其他器件:MSP-FET、

如果我正确阅读了文档(数据表和系列用户指南)、MPS430F5359的四个 JTAG 引脚(TDO、TDI/TCLK、TMS 和 TCK)也可被配置为 GPIO 引脚 PJ.0、PJ.1、PJ.2和 PJ.3。

那么、我编写了一些代码来尝试执行该重新配置、然后操纵引脚。 (您可以轻松地猜测我的各种宏的功能。)

// set_bits (PJOUT,(bit_3 | bit_2 | bit_1 | bit_0));

// SET_BITS( PJDIR,( bit_3| bit_2 | bit_1 | bit_0 ));

PJOUT = 0xFFFFU;

PJDIR = 0xFFFFU;

for (uint16 i = 0;i < 10u;i++)

{

CLR_BIT (PJOUT、BIT_0);

DELAY_US(10UL);

CLR_BIT (PJOUT,BIT_1);

DELAY_US(10UL);

CLR_BIT (PJOUT,bit_2);

DELAY_US(10UL);

CLR_BIT (PJOUT,bit_3);

DELAY_US(10UL);

PJOUT = 0x0000U;

DELAY_US(10UL);

Set_Bit (PJOUT,bit_0);

DELAY_US(10UL);

Set_bit (PJOUT,bit_1);

DELAY_US(10UL);

Set_Bit (PJOUT,bit_2);

DELAY_US(10UL);

Set_bit (PJOUT,bit_3);

DELAY_US(10UL);

PJOUT = 0xFFFFU;

DELAY_US(10UL);

}

但当我运行代码时、只有 TDO (PJ.0)会摆动。

这些文档说明 TEST/SBWTCK 信号对此具有一定的控制、但是当那个引脚被下拉至 VSS 时、GPIO 应该可用;我在电路板上有一个外部逻辑、 IS 下拉该引脚。

本文档还讨论了 SYSCTL 寄存器中的 SYSJTAGPIN 位、但重点是禁用 GPIO、因此我要让该寄存器保持默认 BOR 状态(设置该位似乎会禁用我成功使用 PJ.0)。

注:

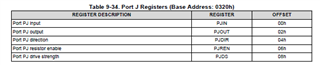

端口 J 没有"SEL"寄存器来选择管脚是 GPIO 还是外设功能引脚。

有人知道为什么我只能得到 PJ.0作为 GPIO 工作、而不能得到 PJ.1、PJ.2或 PJ.3?