主题中讨论的其他器件:TLV320AIC3104、 SN74AVC4T245

您好的支持团队、

对于 AM437x 处理器和编解码器(TLV320AIC3104)之间的信号(McASP)、我有以下问题。

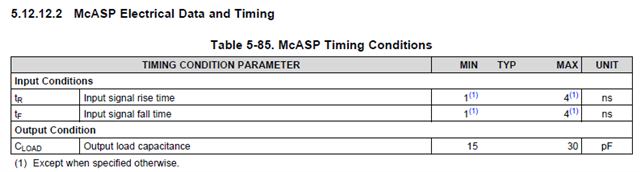

AM437x 数据表指出、以下输入信号的 TR 和 TF 介于1ns 和4ns 之间。

我知道、在论坛的以下回复中、此转换时间指定为10%至90%。

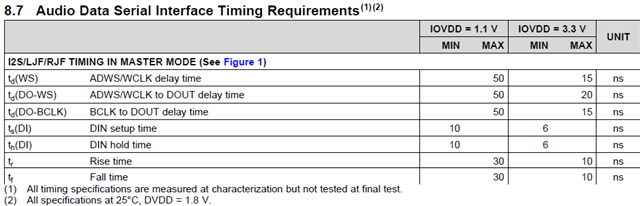

此外、编解码器数据表规定、当 IOVDD=3.3V 时、TR 和 TF 为~10ns。

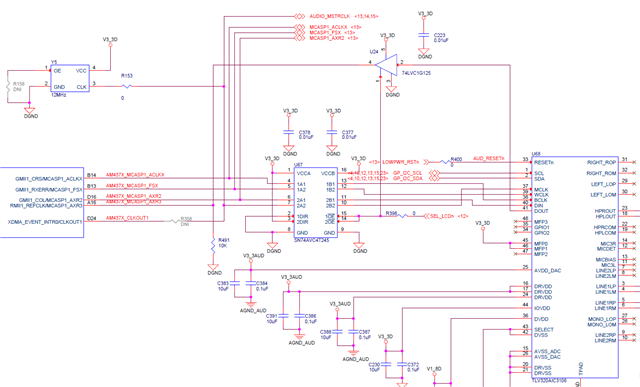

目前、在客户的原型板中、AM437x 处理器和编解码器(TLV320AIC3104)通过 McASP (I2S)进行连接。

信号线(WCLK、BCLK、Din、DOUT)直接连接在 CPU 和编解码器之间、使用编解码器作为主控模式、

但每个信号 WCLK、BCLK、Din、DOUT 的 TR 和 TF 的实际测量值约为15ns、

超过 CPU 和编解码器输入信号转换时间的最大值。

这里有一些问题。

Q1:对于 WCLK、BCLK 和数据时序请求(设置、保持)、15ns 的电流信号转换时间具有足够的裕量、

但这种转换时间是否可以接受?

如果不是、会导致什么问题?

Q2:为了 达到转换时间要求、有必要在 CPU 和编解码器之间添加一个缓冲器。

参考 AM437x 评估板原理图、通过 SN74AVC4T245和74LVC1G125进行连接、如下所示。

SN74AVC4T245和74LVC1G125的数据表 中未提及输出信号的转换时间。

如何确认 CPU McASP 输入信号的转换时间为1ns 至4ns

编解码器的 I2S 输入信号的转换时间为~10ns?

此致、

卡纳