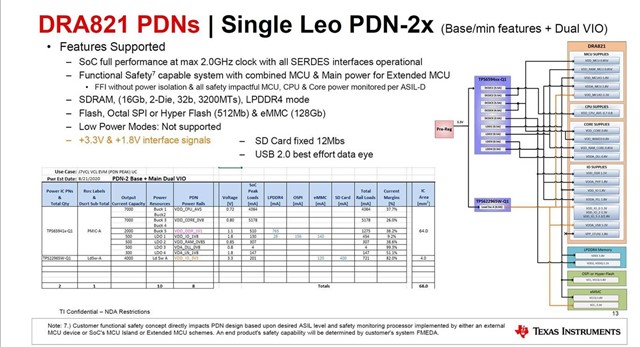

主题中讨论的其他器件:DRA821

香榭丽舍

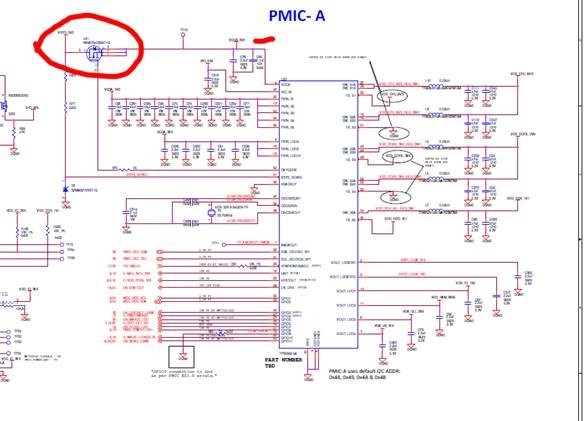

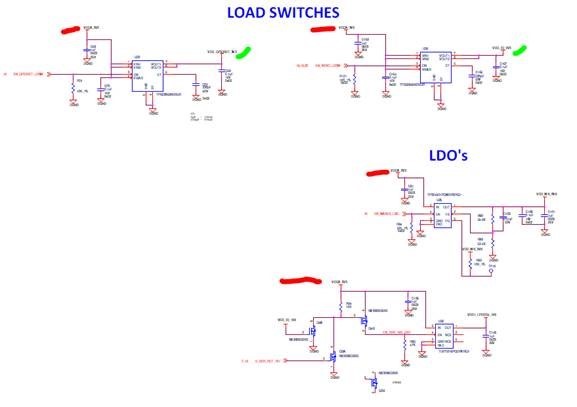

在参考设计中、VDD_WAKE0电源引脚由一个单独的 LDO 供电、该 LDO 由 PMIC 进行切换。 (VDD_WK_0V8)。 为什么要将其连接到已启用开关的 LDO?

是否可以将 LDO 保留在输出状态并将其连接到内核0.8V 电源? DRA821 DS 图8-3中的加电序列显示了它在 T2处与其他0.8V 电压电源(包括内核0V8)一同出现。 数据表还在表10-1中将其与数字低电压框组合在一起

此设计未使用任何低功耗模式、并且始终从冷启动启动开始。

谢谢

Michael