尊敬的 TI 团队:

我有一个与如何计算 TDA2PXEVM McASP 模块的 AUXCLK 值相关的问题。

我尝试使用 PDK 中 CSL 文件夹中提供的 McASP 发送示例:

μ C/processor_sdk_vision_03_08_00_00/ti_compons/drivers/pdk_01_10_04_05/packages/ti/CSL/example/McASP/McASP_transmit ~

我查看 了 TDA2Px 技术参考手册、以及我用来计算 AUXCLK 的以下步骤。

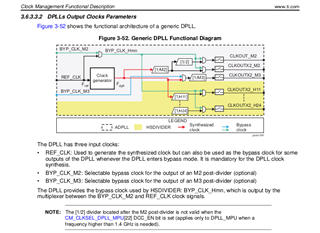

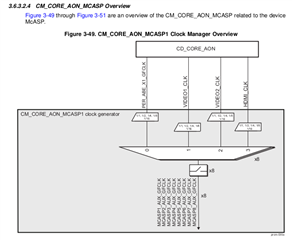

从"3.6.3.2.4 CM_CORE_AON_MCASP 概述"中、我可以看到 McASP3_AUX_GFCLK 的不同可能来源、通过读取"CM_L4PER2_MCASP3_CLKCTRL[23:22] CLKSEL_AUX_CLK"(值0)寄存器、我可以确认"PER_CLK_SOURCE"已使用。

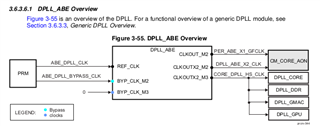

2.从"3.6.3.6.1 DPLL_ABE 概述"中、我可以看到"per_ABE_X1_GFCLK"信号源是通过"DPLL_ABE"模块后的"ABE_DPLL_CLK"信号。

3.从"图3-40. PRM 时钟管理器概述"、我可以看到"ABE_DPLL_CLK"的不同可能来源、并通过读取"CM_CLKSEL_ABE_PLL_REF[0] CLKSEL"(值0)和"CM_CLKSEL_ABE_PLL_SYS[0] CLKSEL"(值1)寄存器、我可以确认"CLK2_SYS"源代码已被使用。

4.从"TDA2Px-ACD CPU EVM 板用户指南"部分的"3.4时钟"中、辅助时钟(OSC1)由22.5792MHz 时钟供源。

5.返回到"DPLL_ABE 模块"、"3.6.3.3.2 DPLL 输出时钟参数"部分介绍了"ABE_DPLL_CLK"输入信号中"PER_ABE_X1_GFCLK"输出信号的分频。

这取决于 CM_CLKMODE_DPLL_ABE[11] DPLL_REGM4XEN 之外的 M、N 和 M2值。

这些值如下:

m "CM_CLKSEL_DPLL_ABE[18:8] DPLL_MULT"为200

n "CM_CLKSEL_DPLL_ABE[6:0] DPLL_DIV"为9

CM_CLKMODE_DPLL_ABE[11] DPLL_REGM4XEN 为0

M2 "CM_DIV_M2_DPLL_ABE[4:0] DIVHS"为1

因此、如果我应用了上述所有源、我可以得到 AUXCLK 等于451.584MHz。

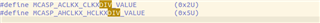

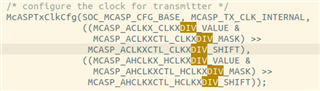

返回到"McASP_Transmit "示例、它声称位 时钟应该为10MHz、方法是使用"CLKXDIV"值2、这会产生值3、而"HCLKXDIV"值5、这会产生值6。

如果 AUXCLK 等于 451.584MHz、 CLKXDIV"值2和"HCLKXDIV"值5、位时钟应该为 25.088MHz、而不是如声明的10MHz

我需要您的帮助来确定我的计算与索赔值不匹配的原因、因为我将取决于我的应用的这些计算。

非常感谢您的意见。

此致、

Ahmed