Thread 中讨论的其他器件:XIO2001

您好!

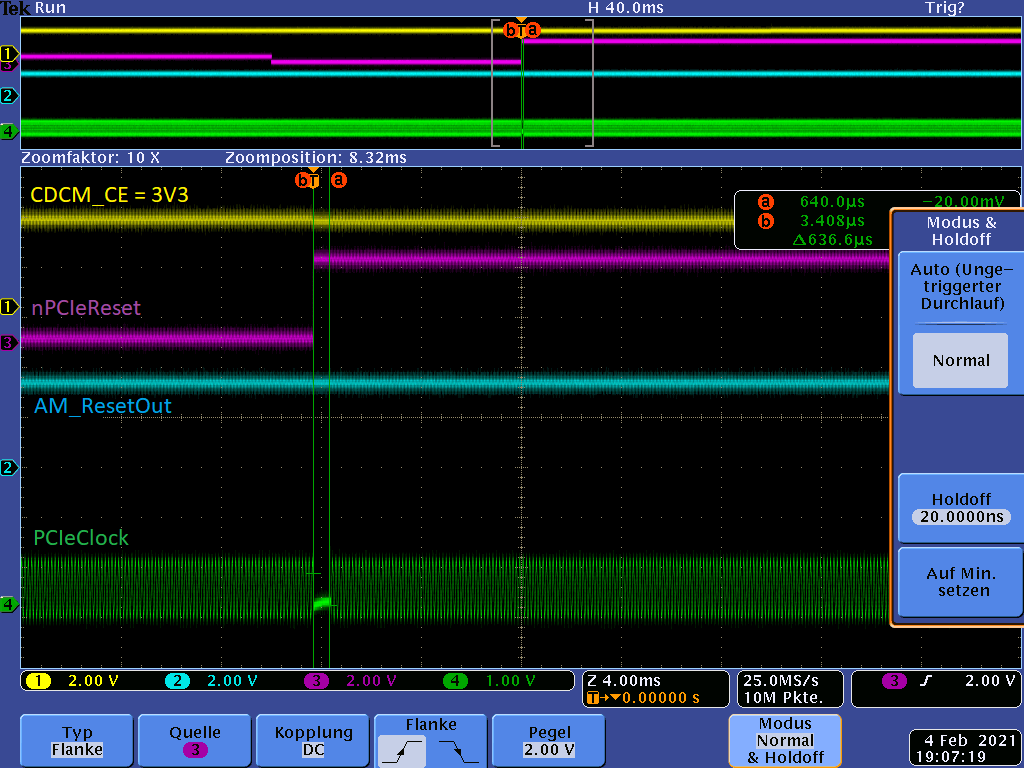

当连接了 PCIe 设备 TI XIO2001 (PCIe/PCI 桥接器)时、系统启动仍然存在问题。

另请参阅票证 https://e2e.ti.com/support/processors/f/791/t/942634

我们系统的简要架构:

nGRST–表示 XIO2001的内部复位。 它仅连接到电容器。

nPCIeReset–此信号由 Sitara 控制。 在本例中、我们添加了一个下拉电阻器、因此信号仅由 CPU 释放

3V3–这是我们的电源电压、正如您看到的、它是稳定的

nPOR (PORz)–由上电和 FPGA 供电的电压芯片控制。 当系统未启动时、我们在 FPGA 中实施看门狗

AM_CDCM_CE–连接到 Sitara 并始终保持稳定

PCIeClockn`t–由于采样频率、我们无法很好地对其进行测量。

当我们想要读取 PCIe 寄存器时、CPU 残桩。

此问题在某些主板(> 10次)和其他主板(相同的硬件和软件)上重复出现,但不会出现。

我们将从 SPI 闪存引导

谢谢、此致

Chris