工具/软件:TI-RTOS

您好!

我们将使用您的 ti-RTOS 超链接示例(无 xDMA 或中断配置)、在某些硬件配置中、我们使用 K2H (使用 RTM BOC 的 EMV 板)和几个 C6657 (仅对 EVM 板进行测试的 HL C6657 HL 连接):

1) 1)内部环路中的 K2H 和 C6657正常工作

2) 2) C6657<->C6657的工作原理

3) K2H <-> C6657在两个 K2H 端口上都不工作(0/1)

当尝试读取远程寄存器时、测试将停止。

我已经测试了一些软件配置:

1) 1) 1通道@ 3.125Gb/s

2) 2) 4条通道@ 6.25Gb/s

3)调试/发布版本

在 K2H 侧、我可以看到以下行为:

版本号:0x02010008;字符串 HYPLNK LLD 修订版本:02.01.00.08:10月 6日2018:02:57:41

即将进行系统设置(PLL、PSC 和 DDR)

已构造 SERDES 配置:PLL=0x00000228;RX=0x0046c495;TX=0x000ccf95

系统设置工作正常

即将设置 HyperLink 外设

=================================== 超链接测试端口0

================================================================================ 在初始化之前开始寄存器===========

修订版寄存器内容:

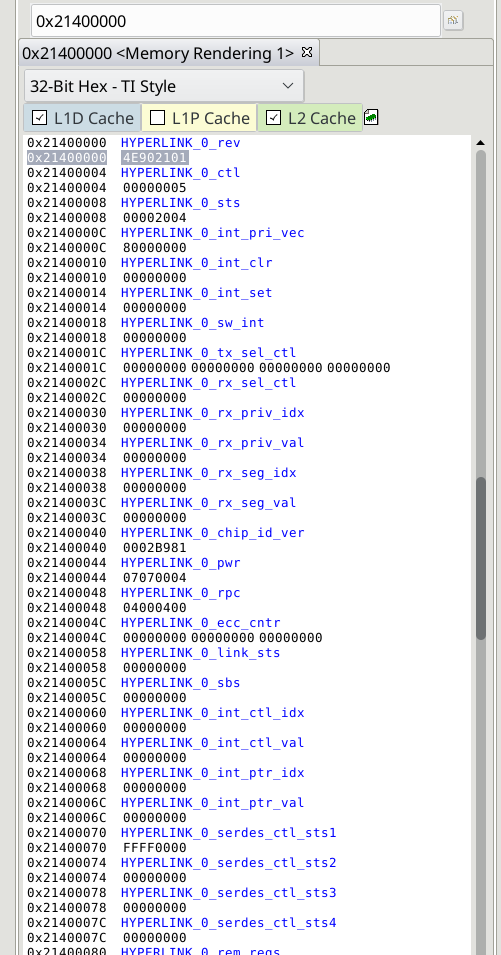

RAW = 0x4e902101

状态寄存器内容:

RAW = 0x00003004

链路状态寄存器内容:

RAW = 0x00000000

控制寄存器内容:

RAW = 0x00000000

控制寄存器内容:

RAW = 0x00000000

=================== 在初始化之前结束寄存器===========

HyperLink Serdes Common Init Complete

而在 C6657侧:

版本号:0x02010006;字符串 HYPLNK LLD 修订版本:02.01.00.06:2017年3月28日:14:26:56

即将进行系统设置(PLL、PSC 和 DDR)

已构造 SERDES 配置:PLL=0x00000064;RX=0x0046c4a5;TX=0x000ccfa5

系统设置工作正常

即将设置 HyperLink 外设

=================================== 超链接测试端口0

================================================================================ 在初始化之前开始寄存器===========

修订版寄存器内容:

RAW = 0x4e901900

状态寄存器内容:

RAW = 0x00000004

链路状态寄存器内容:

RAW = 0x00000000

控制寄存器内容:

RAW = 0x00000000

控制寄存器内容:

RAW = 0x00000000

=================== 在初始化之前结束寄存器===========

等待另一侧升高(0)

SERDES_STS (32位)内容:0x03060c19;LOCK = 1

等待另一侧升高( 1)

等待另一侧升高( 2)

等待另一侧出现 (3)

等待另一侧出现 (4)

等待另一侧出现 (5)

…

SerDes 配置问题、不是吗?

#define hyplnk_example_port 0

#define hyplnk_example_REFCLK_use_PLATCFG

#define hyplnk_example_allow_1_lane

#define hyplnk_example_SERRATE_03p125

#define hyplnk_example_ASYNC_Clocks

#define hyplnk_example_EQ_analysis

#define hyplnk_example_test_cpu_token_exchange

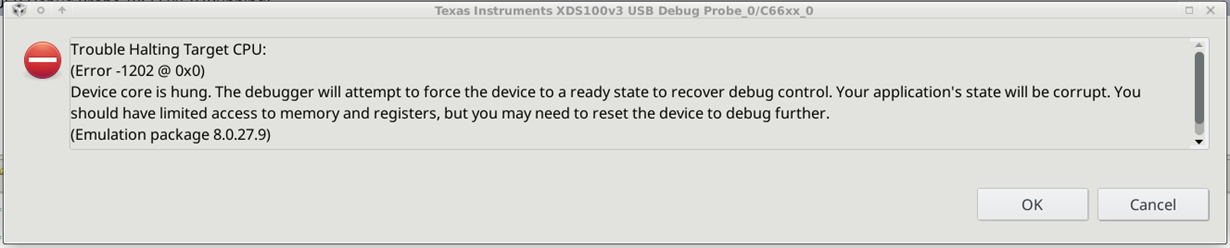

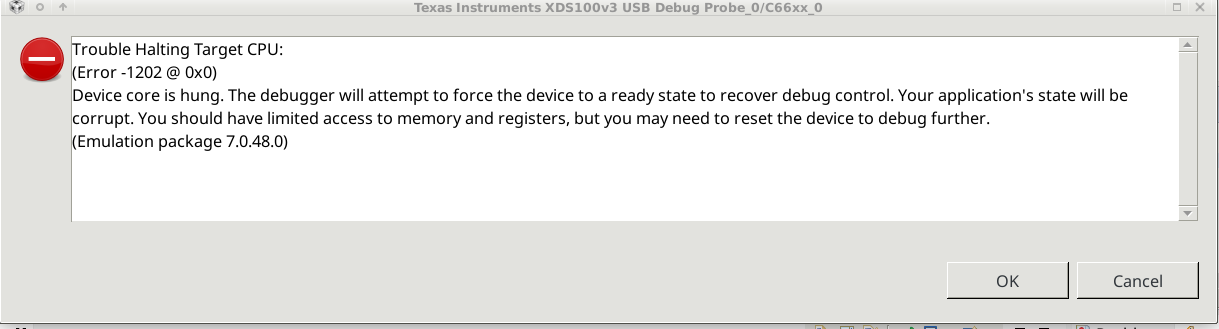

在其他版本(我的代码)中、我更改了一些内容、通道正常工作、但当代码到达读取远程寄存器时、DSP0 (CC6657)将崩溃。

在 K2H 侧:

00:00:20 00:00:20 hyplnkMemoryMapped.c@735: 版本号:0x02010008;字符串 HYPLNK LLD 修订版本:02.01.00.08:OCT 6

2018:02:57:41

00:00:20 00:00:00 hyplnkMemoryMapped.c@746: 即将进行系统设置(PLL、PSC 和 DDR)

00:00:20 00:00:00 hyplnkLLDIFace.c@1036: 构建的 SERDES 配置:PLL=0x00000228;RX=0x0046c495;TX=0x000ccf95

00:00:20 00:00:00 hyplnkMemoryMapped.c@753: 系统设置正常

00:00:20 00:00:00 hyplnkMemoryMapped.c@761: 即将设置超链接外设

00:00:20 00:00:00 hyplnkLLDIFace.c@1605: ===================

00:00:20 00:00:00 hyplnkLLDIFace.c@1606: 超链接测试端口0

00:00:20 00:00:00 hyplnkLLDIFace.c@1607: ===========================

00:00:20 00:00:00 hyplnkLLDIFace.c@1619: === 在初始化之前开始寄存器===========

00:00:20 00:00:00 hyplnkLLDIFace.c@607:修订版寄存器内容: RAW = 0x4e902101

00:00:20 00:00:00 hyplnkLLDIFace.c@656:状态寄存器内容: RAW = 0x00003004

00:00:20 00:00:00 hyplnkLLDIFace.c@699:链路状态寄存器内容: RAW = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@730:控制寄存器内容: RAW = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@752:控制寄存器内容: RAW = 0x00000000

00:00:20 00:00:00 hyplnkLLDIFace.c@1625: =========== 在初始化之前结束寄存器===========

00:00:20 00:00:00 hyplnkLLDIFace.c@534:超链接 Serdes Common Init Complete

00:00:21 00:00:01 hyplnkLLDIFace.c@560:HyperLink 串行器/解串器通道0初始化完成

00:00:21 00:00:00 hyplnkLLDIFace.c@1836: === 初始化后开始寄存器===========

00:00:21 00:00:00 hyplnkLLDIFace.c@656:状态寄存器内容: RAW = 0x04400005

00:00:21 00:00:00 hyplnkLLDIFace.c@699:链路状态寄存器内容: RAW = 0xccf00cf0

00:00:21 00:00:00 hyplnkLLDIFace.c@730:控制寄存器内容: RAW = 0x00004000

00:00:21 00:00:00 hyplnkLLDIFace.c@1840: =========== 初始化后结束寄存器===========

00:00:21 00:00:00 hyplnkMemoryMapped.c@768: 外设设置工作正常

00:00:21 00:00:00 hyplnkLLDIFace.c@1899: 等待5秒以检查链路稳定性

00:00:26 00:00:05 hyplnkLLDIFace.c@1911: 分析每个通道的连接

00:00:26 00:00:00 hyplnkLLDIFace.c@1138: 前体1.

00:00:26 00:00:00 hyplnkLLDIFace.c@1163:

00:00:26 00:00:00 hyplnkLLDIFace.c@1142: 后标:19

00:00:26 00:00:00 hyplnkLLDIFace.c@1163:

00:00:26 00:00:00 hyplnkLLDIFace.c@1915: 链路看起来稳定

00:00:26 00:00:00 hyplnkLLDIFace.c@1917: 即将尝试读取远程寄存器

C6657端:

00:00:08 00:00:08 hyplnkMemoryMapped.c@718: 版本号:0x02010006;字符串 HYPLNK LLD 修订版本:02.01.00.06:2017年3月28日:146

00:00:08 00:00:00 hyplnkMemoryMapped.c@728: 即将进行系统设置(PLL、PSC 和 DDR)

00:00:08 00:00:00 hyplnkLLDIFace.c@971:构造的 SERDES 配置:PLL=0x00000064;RX=0x0046c495;TX=0x000cc795

00:00:08 00:00:00 hyplnkMemoryMapped.c@735: 系统设置工作正常

00:00:08 00:00:00 hyplnkMemoryMapped.c@744: 即将设置 HyperLink 外设

00:00:08 00:00:00 hyplnkLLDIFace.c@1176: ===========================

00:00:08 00:00:00 hyplnkLLDIFace.c@1177: 超链接测试端口0

00:00:08 00:00:00 hyplnkLLDIFace.c@1178: ===========================

00:00:08 00:00:00 hyplnkLLDIFace.c@1190: === 在初始化之前开始寄存器===========

00:00:08 00:00:00 hyplnkLLDIFace.c@597:修订版寄存器内容: RAW = 0x4e901900

00:00:08 00:00:00 hyplnkLLDIFace.c@646:状态寄存器内容: RAW = 0x00000004

00:00:08 00:00:00 hyplnkLLDIFace.c@689:链路状态寄存器内容: RAW = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@720:控制寄存器内容: RAW = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@742:控制寄存器内容: RAW = 0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@1196: === 在初始化之前结束寄存器===========

00:00:08 00:00:00 hyplnkLLDIFace.c@831:SerDes_STS (32位)内容:0x05001429;LOCK = 1

00:00:08 00:00:00 hyplnkLLDIFace.c@781:VUsr_CFGPLL 超链接 SerDes PLL 配置:0x00000064

00:00:08 00:00:00 hyplnkLLDIFace.c@782:VUsr_CFGRX0超链接串行器/解串器接收配置0:0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@783:VUsr_CFGTX0超链接串行器/解串器发送配置0:0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@784:VUsr_CFGRX1超链接串行器/解串器接收配置1:0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@785:VUsr_CFGTX1超链接串行器/解串器发送配置1:0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@786:VUsr_CFGRX2超链接 SerDes 接收配置2:0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@787:VUsr_CFGTX2超链接串行器/解串器发送配置2:0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@788:VUsr_CFGRX3超链接串行器/解串器接收配置3:0x0046c495

00:00:08 00:00:00 hyplnkLLDIFace.c@789:VUsr_CFGTX3超链接串行器/解串器发送配置3:0x000cc795

00:00:08 00:00:00 hyplnkLLDIFace.c@799:芯片版本内容:0x0000b97a

00:00:08 00:00:00 hyplnkLLDIFace.c@801:通道电源管理控制内容:0x07070004

00:00:08 00:00:00 hyplnkLLDIFace.c@803:串行器/解串器控制和状态1内容:0xff0000

00:00:08 00:00:00 hyplnkLLDIFace.c@805:串行器/解串器控制和状态2内容:0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@807:串行器/解串器控制和状态3内容:0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@809:串行器/解串器控制和状态4内容:0x00000000

00:00:08 00:00:00 hyplnkLLDIFace.c@811:链接状态内容:0xccf00cf0

00:00:08 00:00:00 hyplnkLLDIFace.c@1404: =========== 初始化后开始寄存器===========

00:00:08 00:00:00 hyplnkLLDIFace.c@646:状态寄存器内容: RAW = 0x04400005

00:00:08 00:00:00 hyplnkLLDIFace.c@689:链路状态寄存器内容: RAW = 0xccf00cf0

00:00:08 00:00:00 hyplnkLLDIFace.c@720:控制寄存器内容: RAW = 0x00004000

00:00:08 00:00:00 hyplnkLLDIFace.c@1408: === 初始化后结束寄存器===========

00:00:08 00:00:00 hyplnkLLDIFace.c@1409: 等待5秒以检查链路稳定性

00:00:13 00:00:05 hyplnkLLDIFace.c@1425: 链路看起来稳定

00:00:13 00:00:00 hyplnkLLDIFace.c@1426: 即将尝试读取远程寄存器

请帮帮我们。

此致、

Dario