主题中讨论的其他器件: AM3359、 SN74ALVCH16374

你好

我们使用并行 NOR 闪存在多路复用模式下引导 AM5728。

您能否查看相同的原理图。

reference.e2e.ti.com/.../AM5728_5F00_NOR-FLASH.pdf 的相关原理图

此致

Akash Jain

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好

我们使用并行 NOR 闪存在多路复用模式下引导 AM5728。

您能否查看相同的原理图。

reference.e2e.ti.com/.../AM5728_5F00_NOR-FLASH.pdf 的相关原理图

此致

Akash Jain

您好、Akash、

我快速查看了您所附的原理图。

将 DSP_NOR_DQ0连接到 A1是正确的-在 AD 复用模式下、GPMC 使用 AD0来承载 A1地址信号。

我 SPOT 检查了一些其他地址信号、它们看起来对于 AD 复用模式是正确的。

访问 NOR 闪存时、GPMC ADVn_ALE 低电平有效。 它在访问周期开始时为高电平、对于脉冲为低电平、然后在上升沿、存储器/锁存器将锁定地址。

请参阅 AM5728数据表图7-17。 GPMC/多路复用 NOR 闪存-异步读取-单字时序

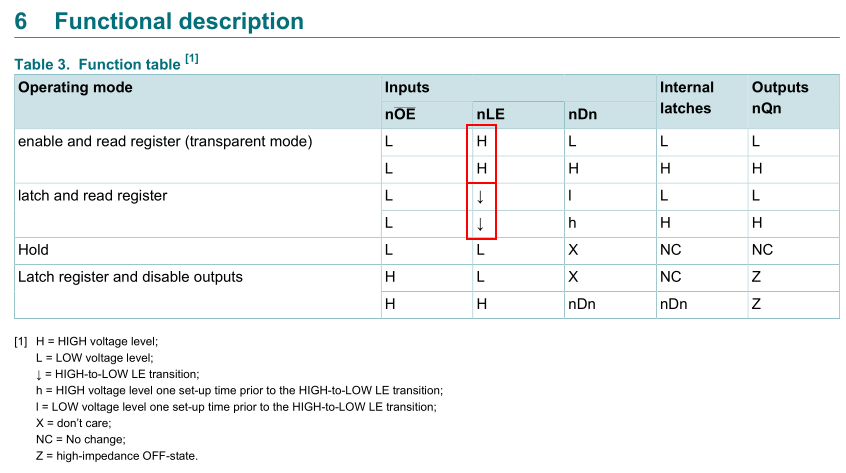

在74ALVT16373上, 当锁存使能(NLE)输入为高电平时、nQn 输出遵循日期(NDN)输入。 闭锁时

使能端变为低电平、nQn 输出在高电平到低电平转换之前的一个设置时间内锁存在 D 输入电平。

我认为您在 NLE 输入之前需要一个逆变器、以便在 ADVn_ALE 的上升沿将输出锁存在输入的电平上。 然后、它们在 ADVn_ALE 为高电平时保持在该状态。

当得到 GPMC 配置寄存器值时、我建议检查环路中锁存器对信号时序的影响。 这些寄存器定义 GPMC 控制信号的时序、地址锁存和数据访问时间。 引导加载程序具有表33-38中介绍的默认设置。 XIP 时序参数。

您计划使用哪种引导模式? 请参阅表33-9。 引导器件顺序以及33.3.7节内存引导。

请注意、引导加载程序仅使用 CS0进行引导。 您可能需要使用差分网配置接头(CH)从该闪存+锁存器引导。 请参阅33.3.8.2配置接头。

我建议在不使用引导加载程序的情况下评估 NOR 闪存。 在尝试从闪存引导加载之前、调试与闪存通信的任何问题。

此致、

标记

您好 Mark

感谢您的快速回顾。

根据您的回答、有一些问题:

DSP_NOR_DQ0 连接到 A1、AD0仅在锁存器上与 DQ0多路复用、因此如何连接或仅正确?

对于 74ALVT16373、它们的 IC 中有内部逆变器、您可以检查一次。

我们只需要使用或引导模式、因此需要对引导引脚进行任何更改?

此外、您能否共享一些参考设计或一些在 AD 多路复用模式下具有 NOR 闪存的评估板?

此致

Akash Jain

您好、Akash、

我认为 GPMC_AD0到 A1和 DQ0的连接是正确的。 很抱歉、如果我弄糊涂了。

我再次检查了74ALVT16373数据表、并确认锁存使能输入为高电平有效、将输入锁存在下降沿(并在高电平时将输入传递到输出)。 对于 NOR 闪烁的低电平有效的 ADVn 信号、这将不起作用。 它需要在 ADVn 的上升沿锁存输入。

请参阅 AM3359 ICE 板(www.ti.com/.../TMDSICE3359)、其中使用锁存器(SN74ALVCH16374)在 AD 多路复用模式下使用 GPMC、其中包含不支持多路复用模式的 NOR 闪存(需要驱动所有地址线路)。 它将 GPMC_ADVn 信号连接到 CLK 输入。 在时钟(CLK)输入的正转换时、触发器的 Q 输出采用数据(D)输入的逻辑电平

我必须让其他更专业的人回答引导加载程序问题。 有关详细信息、请参阅器件 TRM (SPRUHZ6K)。

33.3通过 ROM 代码进行器件初始化

33.3.5外设引导

33.3.6快速外部启动

此致、

标记

您好、Akash、

逆变器将在逻辑上允许这个锁存器在整个写入和读取周期内将地址总线置为内存。

它在输入到反相输出之间引入了2.4ns (典型值)的传播延迟、需要将其纳入计时分析中。

GPMC 当然可以配置为与该逆变器、地址锁存器和 NOR 闪存一起运行。 但是、我不能说引导加载程序将在不执行进一步时序分析的情况下成功引导。

您是否有 AM5728板、可在从 GPMC 引导期间探测 GPMC 信号?

您可以在 GPMC 启动期间研究 GPMC 信号时序、然后运行时序分析、以根据它们的时序要求和开关特性来查看它是否将与逆变器、锁存器和闪存一起运行。

我将与另一位工程师交流、他可能会详细了解引导加载程序的 GPMC 引导模式。

此致、

标记

您好、Akash、

很抱歉耽误你的时间。

我不确定这是否启动闪存+锁存器和逆变器组合。 我建议您使用3个数据表中的数据和我上面所附 TRM 中的表中的 GPMC 配置来计算信号时序是否符合要求。

我的问题是、在 GPMC_FCLK 周期1上、ADVn 被驱动为低电平、然后在 GPMC_FCLK 周期2上驱动为高电平。 该表未指定 WRDATAONADMUXBUS 的值(当 A/D 多路复用器数据总线从地址切换到数据时)、但 WONTIME 设置为3、并且通常对于 AD 多路复用器件、WEONTIME 和 WRDATAONADMUXBUS 是相等的。 在该引导模式期间、可以使用示波器确认这一点。 由于锁存之前有额外的逆变器延迟、因此它会使被延迟的 ADVn 信号锁存的数据总线上的地址保持时间归零。 如果 AD 总线在 GPMC_FCLK 周期3从地址转换为数据、则保持时间将剩余1个 GPMC_FCLK 周期- 2.4ns (典型值)。

AM572x 数据表中的表7-30。 GPMC/NOR 闪存接口开关特性-异步模式编号 FA28还指出、从 GPMC_Wen 有效到数据总线有效的延迟时间最长为2ns。 它不提供最小值、假设为0ns。

如果 GPMC_FCLK 为266MHz (典型值、但可以在此引导模式下通过示波器捕获进行确认)、则 GPMC_FCLK 周期为3.76ns。 锁存器地址的保持时间可能为3.76 - 2.4ns = 1.36ns。 我肯定希望在保持时间方面有更多的裕度。

=-=-

您是否在任何公开可用的电路板中进行了任何搜索以查找或闪存器件? 可能是 TI EVM、E2E 问题或 BeagleBoard 子板。

我没有找到任何具有 A/D 多路复用器和闪存的 AM572x 电路板。 我发现的唯一一个原因是 AM335x ICE 板具有 SN74ALVCH16374DGV 锁存器。 由于此锁存器之前不需要逆变器(锁存器位于由 ADVn_ALE 馈送的时钟上升沿)、因此它不应存在与您的设计中74ALVT16373相同的保持时间问题。 建议您找到不需要外部逆变器的锁存器。

在回答您的问题的过程中、我检查了您的设计中的 sysboot 信号。 拉电阻器和默认跳线位置对于 SD、启用 GPMC 等待的 XIP 引导、启用了16位数据总线的 A/D 多路复用器器件而言看起来很好。 但是、上拉/下拉电阻器旁边的文本并未反映原理图-这有点误导。

请参阅 AM335x_ICE_EVM:M29W160EB NOR -通过 SN74ALVCH16374DGV 传输数据(ALE 为时钟)

http://www.ti.com/lit/df/tidr336/tidr336.zip

此致、

标记