主题中讨论的其他器件:TPS6594-Q1、 DRA829

你(们)好

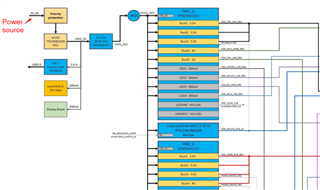

我们遵循 PDN-0C (两个 TPS6594-Q1器件)为 DRA829J 处理器供电。 MCU 和主电压域是隔离的。

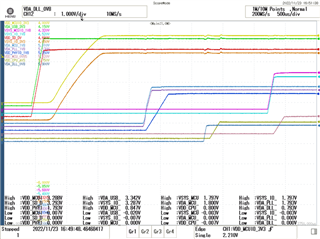

在我们的设计中、加电 排序 是正确的、如下图所示。

匹配 、请参阅 DRA829数据表的第7.10.2.4节。

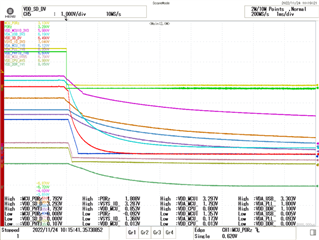

但是、我们的断电顺序存在一些疑问。

如下图所示。

在设计中、我们通过直接断开电源来关闭系统。 但断电排序不匹配 、请参阅 DRA829数据表的第7.10.2.5节。

是否允许此断电排序?

这种不匹配的断电顺序是否会导致一些不可预测的问题?

我们应该如何修改我们的设计?

此致、

储罐