请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM4378 各位专家:

请向 CX 寻求您对此请求的帮助:

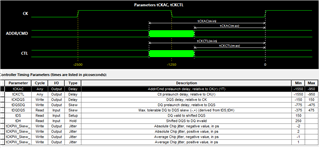

客户正在 Hyperlynx 工具中执行 DDR3L 仿真、 需要将控制器的 DDR 时序模型包含在仿真中。

请求 控制器的 DDR 时序模型(控制 器时序参数模型(.v) Verilog 文件或下面提到的参数)、我们可以在 Hyperlynx 中使用这些模型。

请提供建议。 谢谢你。

此致、

阿尔基·A.