请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM5K2E02 主题中讨论的其他器件: AM5K2E04

您好!

我们正在使用 AM5K2E02处理器开发原型板。 我们当前的断电序列是 在移除输入电源后同时关闭所有电源轨。

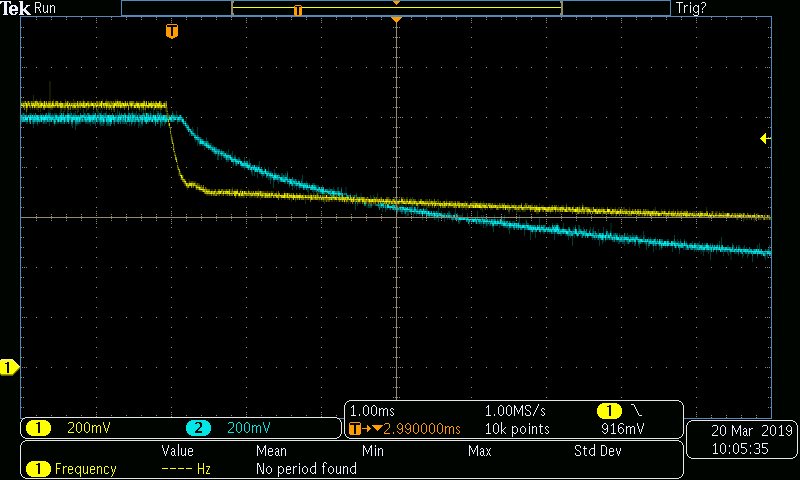

我们在电压轨崩溃时进行了测量、并注意到 CVDD1在 电压降至 CVDD 以下之前大约2ms 大于 CVDD。

这是否会影响处理器的长期可靠性?

其他电源轨看起来不错、但我们是否应该特别注意其他电源轨?

我已附上 示波器波形的屏幕截图、黄色波形为 CVDD、蓝色波形为 CVDD1。

谢谢、

插孔