您好!

我的客户询问我们关于 DDR3设计模式的问题。 您能帮助回答以下问题吗?

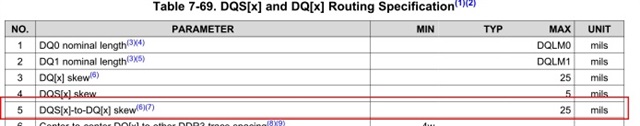

数据表如下表所示。

该表说明"DQS[x]至 DQ[x]偏差"应为最大25mil "。

q1) "mils"表示"mil"(1mil = 0.0254mm)、正确吗?

Q2) 如果是这样,则图案线长度的差异必须小于25mil (0.635mm),正确吗?

如果是、客户认为这是非常苛刻的要求。 它太短了。

Q3) 这是带状线吗? 或微带状线?

Q4) 根据交流时序特性、设置和保持方面似乎有一些裕度。 所以、他们不认为需要相等的长度。

他们想知道25密耳的推导公式。 你能告诉他们吗?

由于电路板尺寸限制、等距接线实际上很困难。 如果应用该值、即使一个层间通孔也会偏离该值。

谢谢。此致、

秀明