请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM3351 您好!

我将为 BeagleBone Black 配置一个器件树以访问双端口 RAM。

我应用了已配置的器件树、但在/proc/iomem.中看不到已分配的内存区域

我使用的是4.14.108-ti-xenomai-r143

下面是 iomem

| root@BeagleBone:/home/skj/dtc_build # cat /proc/iomem 40300000-4030ffff : 40300000.ocmcram 44d00000-44d03fff : umem 44d80000-44d81fff : DMEM 44e07000-44e07fff :/ocp/gpio@44e07000 44e09000-44e0901f:串行 44e0b000-44e0bfff :/ocp/i2c@44e0b000 44e10620-44e1062f:phy_ctrl 44e1068-44e1064b:唤醒 44e10650-44e10653:gmii-sel 44e10800-44e10a37:pinctrl-single 44e10f90-44e10fcf :/ocp/l4_wkup@44c000000000/SCM@210000/dma-router@f90 44e11324-44e11347 :/ocp/l4_wkup@44c000000000/SCM@210000/wkup_m3_IPC@1324. 44e35000-44e35fff :/ocp/wdt@44e35000 44e3e000-44e3efff :/ocp/rtc@44e3e000 47401000-474011ff:控制 47401400-474017ff:MC 47401400-474017ff:MC 47401800-474019ff:控制 47401c00-47401fff : mc. 47401c00-47401fff : mc. 47402000-47402fff:控制器 47403000-47403fff :调度程序 47404000-47407fff :队列管理器 48042000-480423ff :/ocp/timer@48042000 48044000-480443ff :/ocp/timer@48044000 48046000-480463ff :/ocp/timer@48046000 48048000-480483ff :/ocp/timer@48048000 4804a000-4804a3ff :/ocp/timer@4804a000 4804c000-4804cfff :/ocp/gpio@4804c000 48060000-48060fff :/ocp/mmc@48060000 480c8000-480c81ff :/ocp/mailbox@480c8000 4819c000-4819cfff :/ocp/i2c@4819c000 481ac000-481acfff :/ocp/gpio@481ac000 481ae000-481aefff :/ocp/gpio@481ae000 48310000-48311fff :/ocp/rng@48310000 49000000-4900ffff : EDMA3_cc 4a100000-4a1007ff :/ocp/ethernet@4a100000 4a101000-4a1010ff :/ocp/ethernet@4a100000/MDIO@4a101000 4a101200-4a1012ff :/ocp/ethernet@4a100000 4a320000-4a321fff : INTC 4a322000-4a3223ff:控制 4a322400-4a3224ff:调试 4a324000-4a3243ff:控制 4a324400-4a3244ff :调试 4a334000-4a335fff : IRAM. 4a338000-4a339fff : IRAM. 4c000000-4c000fff :/ocp/emif@4c000000 50000000-50001fff :/ocp/gpmc@50000000 53100000-531001ff :/ocp/sham@53100000 53500000-5350009f :/ocp/aes@53500000 80000000-9fdfff:系统 RAM 80008000-812ffff:内核代码 81400000-815b423f:内核数据 |

DTS 如下

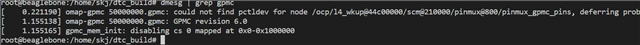

/* * Copyright (C) 2012 Texas Instruments Incorporated - http://www.ti.com/ * * This program is free software; you can redistribute it and/or modify * it under the terms of the GNU General Public License version 2 as * published by the Free Software Foundation. */ /dts-v1/; /plugin/; / { compatible = "ti,beaglebone", "ti,beaglebone-black"; part-number = "dualmemory3"; version = "00A0"; /* state the resources this cape uses */ exclusive-use = /* the pin header uses */ "P9.24", /* mcasp0: mcasp0_ahclkx */ "P9.25", /* mcasp0: mcasp0_axr2 */ "P9.26", /* mcasp0: mcasp0_fsx */ "P9.27", /* mcasp0: mcasp0_aclkx */ "P9.28", /* lcd: lcd_data0 */ "P9.29", /* lcd: lcd_data1 */ "P9.30", /* lcd: lcd_data2 */ "P9.31", /* lcd: lcd_data3 */ "P9.11", /* GPMC WAIT0 */ "P9.13", /* GPMC WPN */ "P8.3", /* GPMC AD6 */ "P8.4", /* GPMC AD7 */ "P8.5", /* GPMC AD2 */ "P8.6", /* GPMC AD3 */ "P8.8", /* GPMC OEN REN */ "P8.10", /* GPMC WEN*/ "P8.11", /* GPMC AD13*/ "P8.12", /* GPMC AD12*/ "P8.13", /* GPMC AD9*/ "P8.14", /* GPMC AD10*/ "P8.15", /* GPMC AD15*/ "P8.16", /* GPMC AD14*/ "P8.17", /* GPMC AD11*/ "P8.19", /* GPMC AD8*/ "P8.22", /* GPMC AD5*/ "P8.23", /* GPMC AD4*/ "P8.24", /* GPMC AD1*/ "P8.25", /* GPMC AD0*/ "P8.26", /* GPMC CSN0*/ "P8.27", /* GPMC A8*/ "P8.28", /* GPMC A10*/ "P8.29", /* GPMC A9*/ "P8.30", /* GPMC A11*/ "P8.37", /* GPMC A12*/ "P8.39", /* GPMC A6*/ "P8.40", /* GPMC A7*/ "P8.41", /* GPMC A4*/ "P8.42", /* GPMC A5*/ "P8.43", /* GPMC A2*/ "P8.44", /* GPMC A3*/ "P8.46", /* GPMC A1*/ "gpio0_31", "gpmc", /* the hardware IP uses */ "gpio0_15", "gpio3_21", "gpio0_14", "gpio3_19", "gpio3_17", "gpio3_15", "gpio3_16", "gpio3_14"; fragment@0 { target = <&am33xx_pinmux>; __overlay__ { gpmc_pins: pinmux_gpmc_pins { status = "okay"; pinctrl-single,pins = < 0x70 0x08 /* gpmc_wait0 */ 0x74 0x17 /* gpmc_wpn(sem-gpio) */ 0x94 0x08 /* gpmc_oen_ren */ 0x98 0x08 /* gpmc_wen */ 0x7c 0x08 /* gpmc_csn0(not used) */ 0x40 0x17 /* gpmc_a0(csn-gpio) */ 0x0 0x30 /* gpmc_ad0 */ 0x4 0x30 /* gpmc_ad1 */ 0x8 0x30 /* gpmc_ad2 */ 0xc 0x30 /* gpmc_ad3 */ 0x10 0x30 /* gpmc_ad4 */ 0x14 0x30 /* gpmc_ad5 */ 0x18 0x30 /* gpmc_ad6 */ 0x1c 0x30 /* gpmc_ad7 */ 0x20 0x30 /* gpmc_ad8 */ 0x24 0x30 /* gpmc_ad9 */ 0x28 0x30 /* gpmc_ad10 */ 0x2c 0x30 /* gpmc_ad11 */ 0x30 0x30 /* gpmc_ad12 */ 0x34 0x30 /* gpmc_ad13 */ 0x38 0x30 /* gpmc_ad14 */ 0x3c 0x30 /* gpmc_ad15 */ 0xa4 0x09 /* lcd_data1(gpmc_a1) */ 0xa8 0x09 /* lcd_data2(gpmc_a2) */ 0xac 0x09 /* lcd_data3(gpmc_a3) */ 0xb0 0x09 /* lcd_data4(gpmc_a4) */ 0xb4 0x09 /* lcd_data5(gpmc_a5) */ 0xb8 0x09 /* lcd_data6(gpmc_a6) */ 0xbc 0x09 /* lcd_data7(gpmc_a7) */ 0xe0 0x09 /* lcd_vsync(gpmc_a8) */ 0xe4 0x09 /* lcd_hsync(gpmc_a9) */ 0xe8 0x09 /* lcd_pclk(gpmc_a10) */ 0xec 0x09 /* lcd_ac_bias_en(gpmc_a11) */ 0xc0 0x09 /* lcd_data8(gpmc_a12) */ >; }; debug_led_pins: pinmux_debug_led_pins { status = "okay"; pinctrl-single,pins = < 0x184 0x17 /* uart1_txd, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x1ac 0x17 /* mcasp0_ahclkx, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x180 0x17 /* uart1_rxd, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x1a4 0x17 /* mcasp0_fsr, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x19c 0x17 /* mcasp0_ahclkr, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x194 0x17 /* mcasp0_fsx, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x198 0x17 /* mcasp0_axr0, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ 0x190 0x17 /* mcasp0_aclkx, OMAP_MUX_MODE7 | AM33XX_PIN_OUTPUT | AM33XX_PULL_ENA */ >; }; }; }; fragment@1 { target = <&ocp>; __overlay__ { debug-leds { compatible = "gpio-leds"; test-led1 { label = "test-led1"; gpios = <&gpio0 15 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led2 { label = "test-led2"; gpios = <&gpio3 21 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led3 { label = "test-led3"; gpios = <&gpio0 14 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led4 { label = "test-led4"; gpios = <&gpio3 19 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led5 { label = "test-led5"; gpios = <&gpio3 17 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led6 { label = "test-led6"; gpios = <&gpio3 15 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led7 { label = "test-led7"; gpios = <&gpio3 16 0>; linux,default-trigger = "default-on"; default-state = "on"; }; test-led8 { label = "test-led8"; gpios = <&gpio3 14 0>; linux,default-trigger = "default-on"; default-state = "on"; }; }; }; }; fragment@2 { target = <&gpmc>; depth = <1>; /* only create devices on depth 1 */ /* stupid warnings */ #address-cells = <1>; #size-cells = <1>; __overlay__ { status = "okay"; #address-cells = <2>; #size-cells = <1>; pinctrl-names = "default"; pinctrl-0 = <&gpmc_pins>; /*gpmc,num-waitpins = <1>; */ /*gpmc,num-cs = <2>;*/ /* chip select ranges */ ranges = <0 0 0x08000000 0x00100000>; nor{ compatible = "dualport_ram"; status = "okay"; reg = <0 0 0x00100000>; /*gpmc,burst-write;*/ /*gpmc,burst-read;*/ /*gpmc,burst-wrap;*/ bank-width = <2>; gpmc,cs-on-ns = <0>; gpmc,cs-rd-off-ns = <100>; gpmc,cs-wr-off-ns = <40>; gpmc,adv-on-ns = <0>; /* CONFIG3 */ gpmc,adv-rd-off-ns = <20>; gpmc,adv-wr-off-ns = <20>; gpmc,we-on-ns = <20>; /* CONFIG4 */ gpmc,we-off-ns = <40>; gpmc,oe-on-ns = <20>; gpmc,oe-off-ns = <100>; gpmc,page-burst-access-ns = <20>; /* CONFIG 5 */ gpmc,access-ns = <80>; gpmc,rd-cycle-ns = <120>; gpmc,wr-cycle-ns = <60>; gpmc,wr-access-ns = <40>; /* CONFIG 6 */ gpmc,wr-data-mux-bus-ns = <20>; /*gpmc,sync-read; /* GPMC_CONFIG1_READTYPE_ASYNC */ /*gpmc,sync-write; /* GPMC_CONFIG1_WRITETYPE_ASYNC */ /*gpmc,clk-activation-ns = <0>; /* GPMC_CONFIG1_CLKACTIVATIONTIME(2) */ gpmc,device-width = <2>; /* gpmc,burst-length = <16>; gpmc,burst-read; gpmc,burst-write; /*gpmc,mux-add-data = <2>; /* GPMC_CONFIG1_MUXTYPE(2) */ /*gpmc,sync-clk-ps = <20000>; /* CONFIG2 */ /*gpmc,bus-turnaround-ns = <40>;*/ /* CONFIG6:3:0 = 4 */ /*gpmc,cycle2cycle-samecsen;*/ /* CONFIG6:7 = 1 */ /*gpmc,cycle2cycle-delay-ns = <40>;*/ /* CONFIG6:11:8 = 4 */ /* not using dma engine yet, but we can get the channel number here */ dmas = <&edma 1>; dma-names = "dualport"; }; }; }; };

如何通过 GPMC 使用双端口 RAM?

谢谢你。

子。